Sequential consistency (SC) requires that all reads and writes appear to have executed in some total order.

Question:

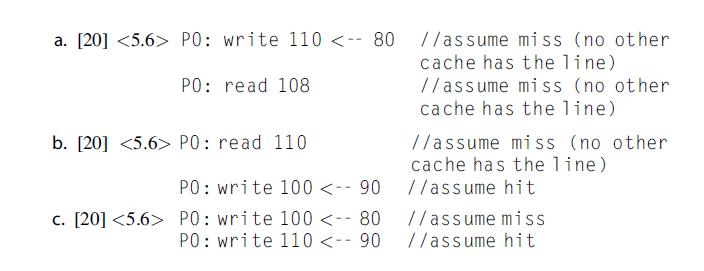

Sequential consistency (SC) requires that all reads and writes appear to have executed in some total order. This may require the processor to stall in certain cases before committing a read or write instruction. Consider the code sequence

![]()

where the write A results in a cache miss and the read B results in a cache hit.

Under SC, the processor must stall read B until after it can order (and thus perform)

write A. Simple implementations of SC will stall the processor until the cache receives the data and can perform the write.

Release consistency (RC) consistency mode relaxes these constraints: ordering—when desired—is enforced by judicious use of synchronization operations. This allows, among other optimizations, processors to implement write buffers, which hold committed writes that have not yet been ordered with respect to other processors’ writes. Reads can pass (and potentially bypass)

the write buffer in RC (which they could not do in SC).

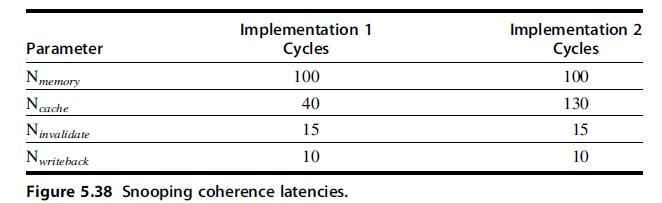

Assume that one memory operation can be performed per cycle and that operations that hit in the cache or that can be satisfied by the write buffer introduce no stall cycles. Operations that miss incur the latencies listed in Figure 5.38.

How many stall cycles occur prior to each operation for both the SC and RC consistency models? (Write buffer can hold at most one write.)

Step by Step Answer:

Computer Architecture A Quantitative Approach

ISBN: 9780128119051

6th Edition

Authors: John L. Hennessy, David A. Patterson