A serial 2s complementer is to be designed. A binary integer of arbitrary length is presented to

Question:

A serial 2s complementer is to be designed. A binary integer of arbitrary length is presented to the serial 2s complementer, least signiicant bit irst, on input X. When a given bit is presented on input X, the corresponding output bit is to appear during the same clock cycle on output Z. To indicate that a sequence is complete and that the circuit is to be initialized to receive another sequence, input Y becomes 1 for one clock cycle. Otherwise, Y is 0.

(a) Find the state diagram for the serial 2s complementer.

(b) Find the state table for the serial 2s complementer.

(c) Write an HDL description for the state machine for the odd parity generator using Example 4-13 (VHDL) or Example 4-15 (Verilog) as a template.

Example 4-13:

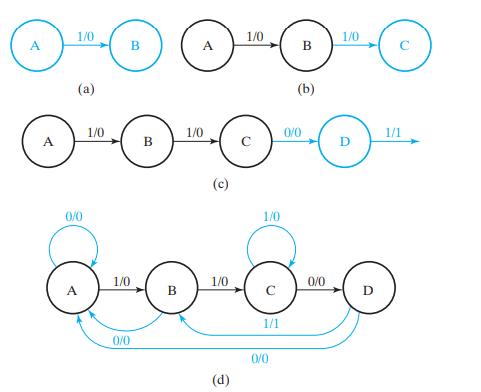

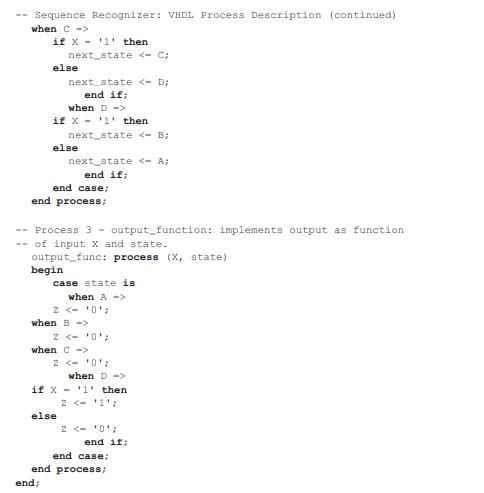

A more complex example in Figures 4-30 and 4-31 represents the sequence- recognizer state diagram in Figure 4-18(d). The architecture in this description consists of three distinct processes, which can execute simultaneously and interact via shared signal values. New concepts included are type declarations for defining new types and case statements for handling conditions.

Figure 4-18(d):

Figure 4-30:

Figure 4-31:

The type declaration permits us to deine new types analogous to existing types such as std_logic. A type declaration begins with the keyword type followed by the name of the new type, the keyword is, and, within parentheses, the list of values for signals of the new type. Using the example from Figure 4-30, we have type state_type is (A, B, C, D);

The name of the new type is state_type and the values in this case are the names of the states in Figure 4-18(d). Once a type has been declared, it can be used for declaring signals or variables. From the example in Figure 4-30,..............

Step by Step Answer:

Logic And Computer Design Fundamentals

ISBN: 9780133760637

5th Edition

Authors: M. Morris Mano, Charles Kime, Tom Martin