For problem in this section, unless otherwise stated, when converting an HLSM to a controller and data

Question:

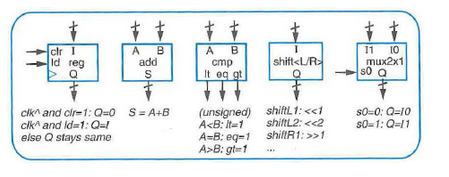

For problem in this section, unless otherwise stated, when converting an HLSM to a controller and data path, derive the controller's FSM and only use data path components from the data path component library of Figure 5.21. Use the RTL design process to create a 4-bit up-counter with input cnt (1 means count up), clear input clr, a terminal count output tc, and a 4-bit output Q indicating, the present count. Only use data path components from Figure 5.21. After deriving the controller's FSM implement the controller as a state register and combinational logic. Requiring a controller and data path pair:

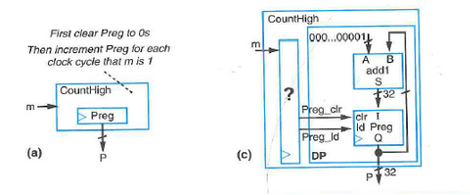

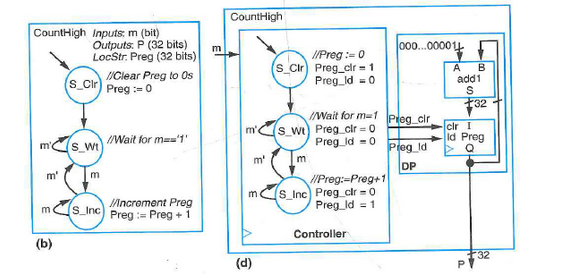

(a) Desired behavior.

(b) HLSM description of desired behavior (LocStr means Local storage),

(c) Data path with potential to implement behavior, but requiring time-varying setting of the data path?s control signal values that should be set in each state to achieve behavior

Figure 5.21 A basic data path component library.

Statistics Principles and Methods

ISBN: 978-0470904114

7th edition

Authors: Richard A. Johnson, Gouri K. Bhattacharyya