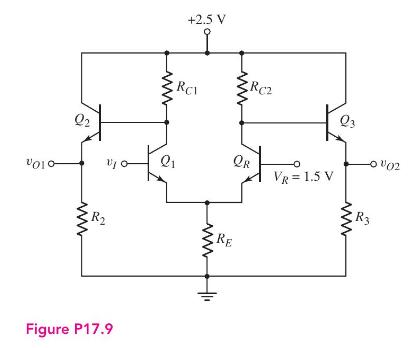

In the ECL circuit in Figure P17.9, the outputs have a logic swing of (0.60 mathrm{~V}), which

Question:

In the ECL circuit in Figure P17.9, the outputs have a logic swing of \(0.60 \mathrm{~V}\), which is symmetrical about the reference voltage. Neglect base currents. The maximum emitter current for all transistors is \(0.8 \mathrm{~mA}\). Assume the input logic voltages \(v_{I}\) are compatible with the output logic voltage. Determine all resistor values.

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Related Book For

Microelectronics Circuit Analysis And Design

ISBN: 9780071289474

4th Edition

Authors: Donald A. Neamen

Question Posted: