In many systems various delays are required. In this project you will create a four bit...

Fantastic news! We've Found the answer you've been seeking!

Question:

Transcribed Image Text:

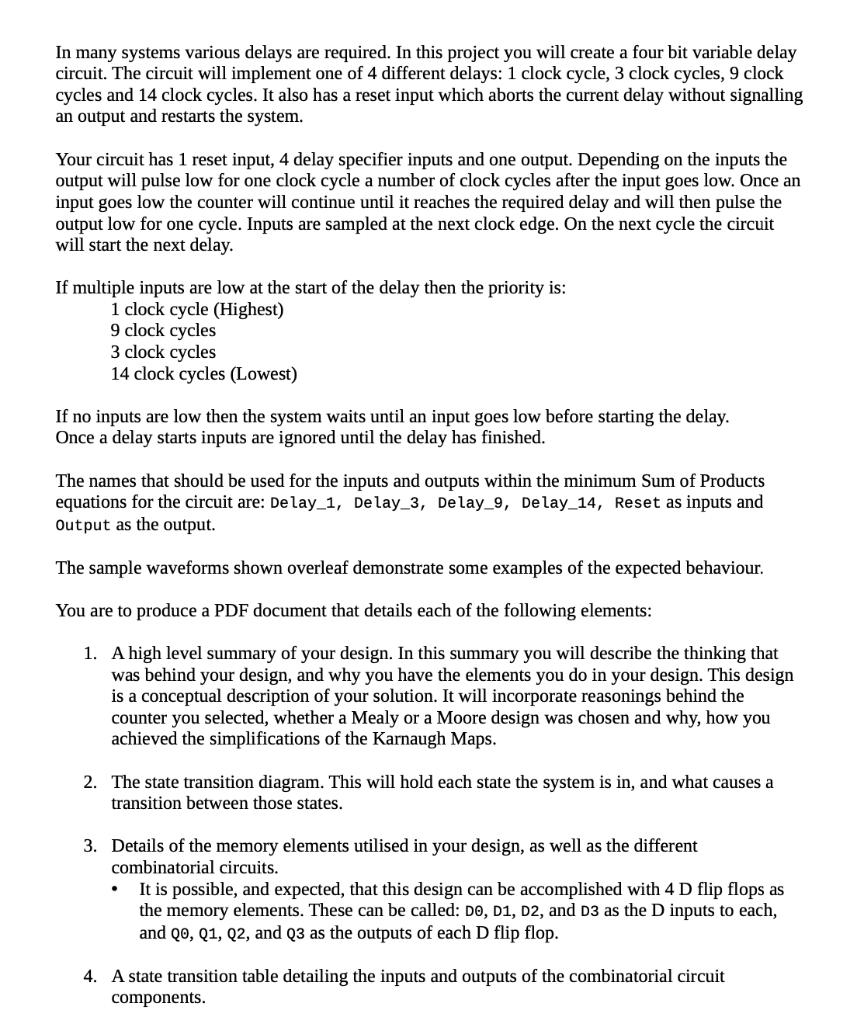

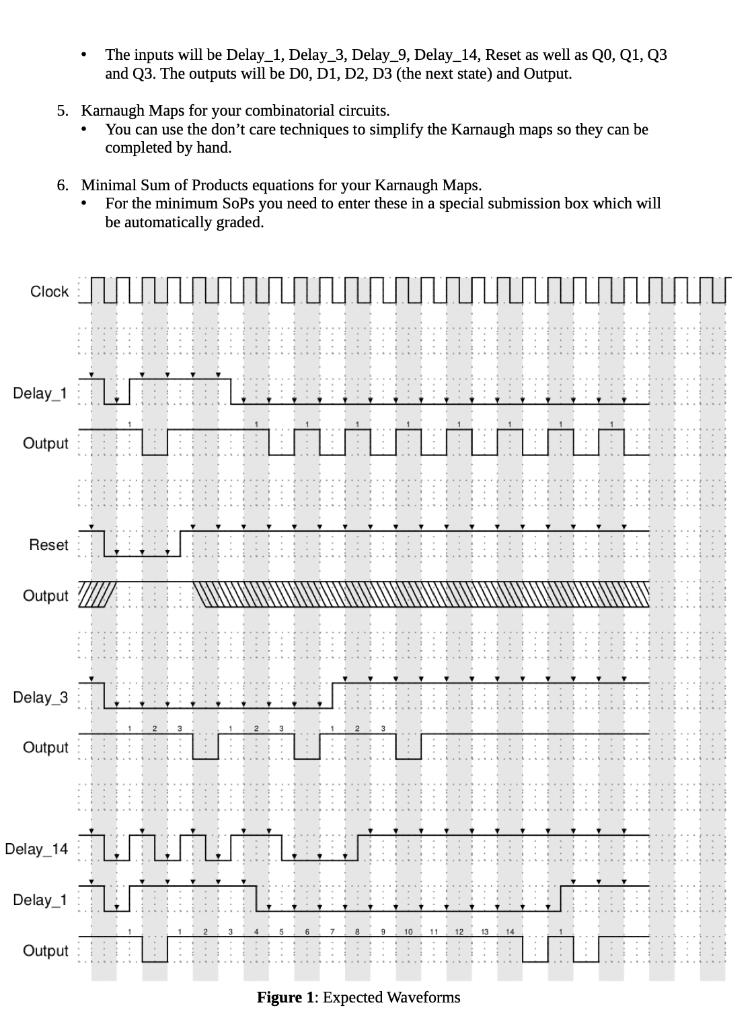

In many systems various delays are required. In this project you will create a four bit variable delay circuit. The circuit will implement one of 4 different delays: 1 clock cycle, 3 clock cycles, 9 clock cycles and 14 clock cycles. It also has a reset input which aborts the current delay without signalling an output and restarts the system. Your circuit has 1 reset input, 4 delay specifier inputs and one output. Depending on the inputs the output will pulse low for one clock cycle a number of clock cycles after the input goes low. Once an input goes low the counter will continue until it reaches the required delay and will then pulse the output low for one cycle. Inputs are sampled at the next clock edge. On the next cycle the circuit will start the next delay. If multiple inputs are low at the start of the delay then the priority is: 1 clock cycle (Highest) 9 clock cycles 3 clock cycles 14 clock cycles (Lowest) If no inputs are low then the system waits until an input goes low before starting the delay. Once a delay starts inputs are ignored until the delay has finished. The names that should be used for the inputs and outputs within the minimum Sum of Products equations for the circuit are: De lay_ 1, Delay 3, Delay_9, Delay_14, Reset as inputs and Output as the output. The sample waveforms shown overleaf demonstrate some examples of the expected behaviour. You are to produce a PDF document that details each of the following elements: 1. A high level summary of your design. In this summary you will describe the thinking that was behind your design, and why you have the elements you do in your design. This design is a conceptual description of your solution. It will incorporate reasonings behind the counter you selected, whether a Mealy or a Moore design was chosen and why, how you achieved the simplifications of the Karnaugh Maps. 2. The state transition diagram. This will hold each state the system is in, and what causes a transition between those states. 3. Details of the memory elements utilised in your design, as well as the different combinatorial circuits. . It is possible, and expected, that this design can be accomplished with 4 D flip flops as the memory elements. These can be called: D0, D1, D2, and D3 as the D inputs to each, and Qo, Q1, Q2, and Q3 as the outputs of each D flip flop. 4. A state transition table detailing the inputs and outputs of the combinatorial circuit components. 5. Karnaugh Maps for your combinatorial circuits. You can use the don't care techniques to simplify the Karnaugh maps so they can be completed by hand. 6. Minimal Sum of Products equations for your Karnaugh Maps. For the minimum SoPs you need to enter these in a special submission box which will be automatically graded. Clock: Delay 1 Output Reset Output Delay 3 Output Delay 14 Delay 1 The inputs will be Delay_1, Delay_3, Delay_9, Delay_14, Reset as well as Q0, Q1, Q3 and Q3. The outputs will be D0, D1, D2, D3 (the next state) and Output. Output . 8 9 10 11 m 12 Figure 1: Expected Waveforms 13 14 ମuuuuu In many systems various delays are required. In this project you will create a four bit variable delay circuit. The circuit will implement one of 4 different delays: 1 clock cycle, 3 clock cycles, 9 clock cycles and 14 clock cycles. It also has a reset input which aborts the current delay without signalling an output and restarts the system. Your circuit has 1 reset input, 4 delay specifier inputs and one output. Depending on the inputs the output will pulse low for one clock cycle a number of clock cycles after the input goes low. Once an input goes low the counter will continue until it reaches the required delay and will then pulse the output low for one cycle. Inputs are sampled at the next clock edge. On the next cycle the circuit will start the next delay. If multiple inputs are low at the start of the delay then the priority is: 1 clock cycle (Highest) 9 clock cycles 3 clock cycles 14 clock cycles (Lowest) If no inputs are low then the system waits until an input goes low before starting the delay. Once a delay starts inputs are ignored until the delay has finished. The names that should be used for the inputs and outputs within the minimum Sum of Products equations for the circuit are: De lay_ 1, Delay 3, Delay_9, Delay_14, Reset as inputs and Output as the output. The sample waveforms shown overleaf demonstrate some examples of the expected behaviour. You are to produce a PDF document that details each of the following elements: 1. A high level summary of your design. In this summary you will describe the thinking that was behind your design, and why you have the elements you do in your design. This design is a conceptual description of your solution. It will incorporate reasonings behind the counter you selected, whether a Mealy or a Moore design was chosen and why, how you achieved the simplifications of the Karnaugh Maps. 2. The state transition diagram. This will hold each state the system is in, and what causes a transition between those states. 3. Details of the memory elements utilised in your design, as well as the different combinatorial circuits. . It is possible, and expected, that this design can be accomplished with 4 D flip flops as the memory elements. These can be called: D0, D1, D2, and D3 as the D inputs to each, and Qo, Q1, Q2, and Q3 as the outputs of each D flip flop. 4. A state transition table detailing the inputs and outputs of the combinatorial circuit components. 5. Karnaugh Maps for your combinatorial circuits. You can use the don't care techniques to simplify the Karnaugh maps so they can be completed by hand. 6. Minimal Sum of Products equations for your Karnaugh Maps. For the minimum SoPs you need to enter these in a special submission box which will be automatically graded. Clock: Delay 1 Output Reset Output Delay 3 Output Delay 14 Delay 1 The inputs will be Delay_1, Delay_3, Delay_9, Delay_14, Reset as well as Q0, Q1, Q3 and Q3. The outputs will be D0, D1, D2, D3 (the next state) and Output. Output . 8 9 10 11 m 12 Figure 1: Expected Waveforms 13 14 ମuuuuu

Expert Answer:

Answer rating: 100% (QA)

This project involves designing a circuit to implement a multidelay system The task is to create a state machine that can output different delays base... View the full answer

Related Book For

Posted Date:

Students also viewed these electrical engineering questions

-

W&S Partners began the planning phase of the Cloud 9 audit. As part of the risk assessment phase for the new audit, the audit team needs to gain an understanding of Cloud 9's structure and its...

-

Answer the following questions based on the accompanying diagram.a. How much would the firm??s revenue change if it lowered price from $12 to $10? Is demand elastic or inelastic in this range?b. How...

-

Answer the following questions based on two assumptions: (1) Inflation increases the prices of all goods by 20%. (2) Ina's income increases from $50,000 to $55,000. a. Has Ina's budget line become...

-

What are the uses of performance appraisal?

-

1. What is the appropriate Box-Jenkins model to use on the original data? 2. What are your forecasts for the first four weeks of January 1983? 3. How do these forecasts compare with actual sales? 4....

-

Refer to Exercise 10.12 and the simple linear regression relating the sweetness index (y) of an orange juice sample to the amount of water soluble pectin (x) in the juice. Find a 90% confidence...

-

The payroll register is a key source of information for computing employer payroll taxes. True/False

-

The Museum of America is preparing for its annual appreciation dinner for contributing members. Last year, 525 members attended the dinner. Tickets for the dinner were $24 per attendee. The profit...

-

Manila Bread Company uses the Conventional retail method to estimate its ending inventories. The following data has been summarized for the year 2018: Cost Retail Inventory, January 1 $54,205 $78,000...

-

Determine the forces in members AB , AC , and AD . Point M is the centroid of triangle BCD . The forces are positive if in tension, negative if in compression. B 5.2' M 5.2' 1190 lb x D 5.2 6.6'

-

BUS 150 Introduction to Financial Accounting Final Assessment Guide Purpose of This Assessment The final assessment for this competency is to identify the various characteristics of financial...

-

The client is diagnosed with inflammation of the glomerulus of the kidney. What is this condition called?

-

Drywell Limited is a USD-based oil company producing one million barrels of oil in Tunisia every year. The annual sales revenue depends on the world oil price. Drywell's cash-flow need for...

-

Problem 4: A boxer punches a 50-kg bag. Just as his fist hits the bag, it travels at a speed of 7 m/sec. As a result of hitting the bag, his hand comes to a complete stop. Assuming that the moving...

-

Explain how economic principles can be applied to this issue to effectively guidedecision making. Demonstrate how supply and demand curves are used to accurately assess the issue. Analyze how the...

-

What is the major factor that will cause a Bow Echo to develop over a squall line?

-

The point (3,-5) is reflected over the x-axis. What are the coordinates of the new point? 2 answers

-

Write a paper about medication error system 2016.

-

You are a CA employed at B & B, Chartered Accountants. On November 20, 2012, the partner in your firm sends you the following e-mail: Our firm has been reappointed auditors of Floral Impressions Ltd....

-

Explain the difference between limitation of scope and disagreement with those charged with governance.

-

What are the four types of tests of controls? Explain them and comment on the reliability of the evidence obtained from each.

-

The rules of conduct of CAs, CGAs, and CMAs require them to report a breach of the rules of conduct by a member to their profession's disciplinary body. What should they do before making such a...

-

The auditor's working papers usually can be pro vided to someone else only with the permission of the client. What is the rationale for such a rule?

-

Many people believe that a public accountant cannot be truly independent when payment of fees is dependent on the management of the client. Explain a way of reducing this appearance of lack of...

Study smarter with the SolutionInn App