The CMOS circuit of Fig. 9.56 is to be used as a high-slew-rate op amp. A load

Question:

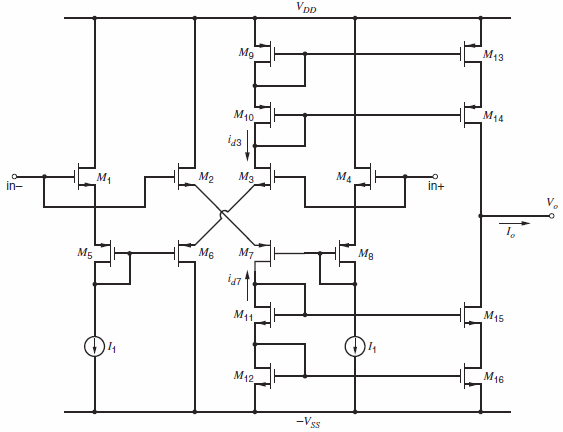

Figure 9.56:

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Related Book For

Analysis and Design of Analog Integrated Circuits

ISBN: 978-0470245996

5th edition

Authors: Paul R. Gray, Paul J. Hurst Stephen H. Lewis, Robert G. Meyer

Question Posted: