Most interrupt handling systems are implemented in the operating system. What hardware support could be added to

Question:

Most interrupt handling systems are implemented in the operating system. What hardware support could be added to make interrupt handling more efficient? Contrast your solution to potential hardware support for function calls.

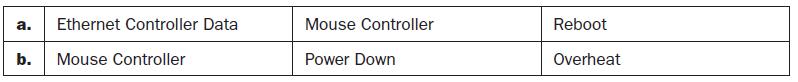

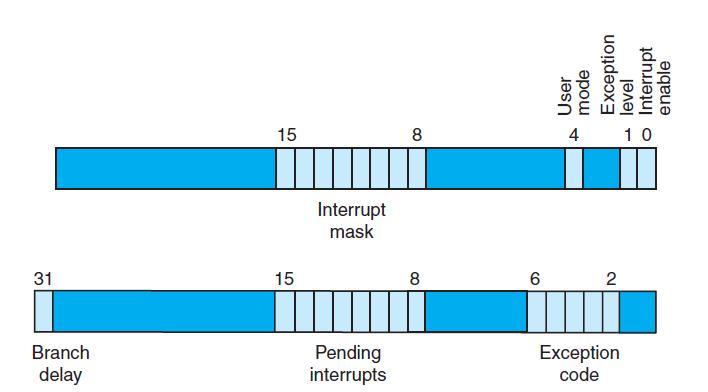

Section 6.6 defines an eight-step process for handling interrupts. The Cause and Status registers together provide information on the cause of the interrupt and the status of the interrupt handling system. Explore interrupt handling by answering the questions about the following combinations of interrupts.

Data From Section 6.6

1. Logically AND the pending interrupt field and the interrupt mask field to see which enabled interrupts could be the culprit. Copies are made of these two registers using the mfc0 instruction.

2. Select the higher priority of these interrupts. The software convention is that the leftmost is the highest priority. 3. Save the interrupt mask field of the Status register.

3. Save the interrupt mask field of the Status register.

4. Change the interrupt mask field to disable all interrupts of equal or lower priority.

5. Save the processor state needed to handle the interrupt.

6. To allow higher-priority interrupts, set the interrupt enable bit of the Cause register to 1.

7. Call the appropriate interrupt routine.

8. Before restoring state, set the interrupt enable bit of the Cause register to 0. This allows you to restore the interrupt mask field.

Step by Step Answer:

Computer Organization And Design The Hardware Software Interface

ISBN: 9780123747501

4th Revised Edition

Authors: David A. Patterson, John L. Hennessy