What is the cycle time for the circuit you designed in 4.5.2? What is the speedup achieved

Question:

What is the cycle time for the circuit you designed in 4.5.2? What is the speedup achieved by using this circuit instead of the one from 4.5.1 for a 32-bit operation?

Problem 4.5.1

Design a circuit with 1-bit data inputs and a 1-bit data output that accomplishes this operation serially, starting with the least-significant bit. In a serial implementation, the circuit is processing input operands bit by bit, generating output bits one by one. For example, a serial AND circuit is simply an AND gate; in cycle N we give it the Nth bit from each of the operands and we get the Nth bit of the result. In addition to data inputs, the circuit has a Clk (clock) input and a "Start" input that is set to 1 only in the very first cycle of the operation. In your design, you can use D Flip-Flops and NOT, AND, OR, and XOR gates.

Problem 4.5.2

Repeat 4.5.1, but now design a circuit that accomplishes this operation 2 bits at a time.

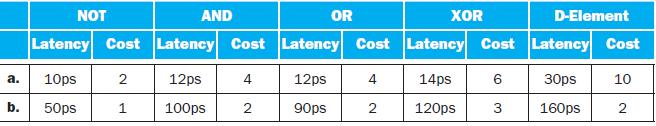

In the rest of this exercise, we assume that the following basic digital logic elements are available, and that their latency and cost are as follows:

The time given for a D-element is its setup time. The data input of a lip-lop must have the correct value one setup-time before the clock edge (end of clock cycle) that stores that value into the lip-lop.

Step by Step Answer:

Computer Organization And Design The Hardware Software Interface

ISBN: 9780123747501

4th Revised Edition

Authors: David A. Patterson, John L. Hennessy