Which pipeline stages can you slow down and by how much, without affecting the clock cycle time?

Question:

Which pipeline stages can you slow down and by how much, without affecting the clock cycle time?

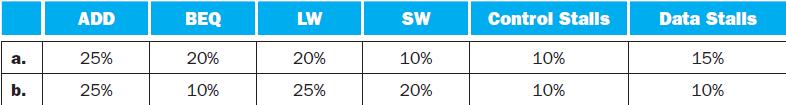

Problems in this exercise assume that, during an execution of the program, processor cycles are spent in the following way. A cycle is "spent" on an instruction if the processor completes that type of instruction in that cycle; a cycle is "spent" on a stall if the processor could not complete an instruction in that cycle because of a stall.

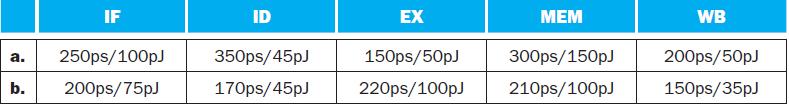

Problems in this exercise also assume that individual pipeline stages have the following latency and energy consumption. The stage expends this energy in order to do its work within the given latency. Note that no energy is spent in the MEM stage during a cycle in which there is no memory access. Similarly, no energy is spent in the WB stage in a cycle in which there is no register write. In several of the following problems, we make assumptions about how energy consumption changes if a stage performs its work slower or faster than this.

Step by Step Answer:

Computer Organization And Design The Hardware Software Interface

ISBN: 9780123747501

4th Revised Edition

Authors: David A. Patterson, John L. Hennessy