Question: For the cache in Problem 6.12, list all of the hexadecimal memory addresses that will hit in set 3. Problem 6.12 The problems that follow

For the cache in Problem 6.12, list all of the hexadecimal memory addresses that will hit in set 3.

Problem 6.12

The problems that follow will help reinforce your understanding of how caches work. Assume the following:

. The memory is byte addressable.

. Memory accesses are to 1-byte words (not to 4-byte words).

. Addresses are 13 bits wide.

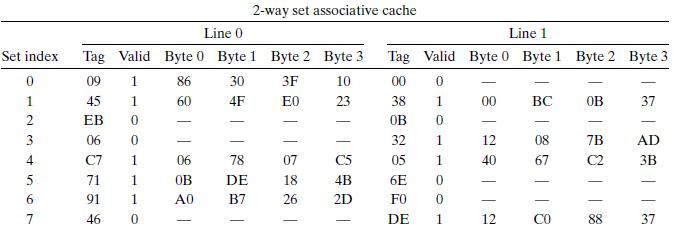

. The cache is two-way set associative (E = 2), with a 4-byte block size (B = 4) and eight sets (S = 8).

The contents of the cache are as follows, with all numbers given in hexadecimal notation.

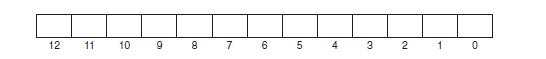

The following figure shows the format of an address (1 bit per box). Indicate (by labeling the diagram) the fields that would be used to determine the following:

CO. The cache block offset

CI. The cache set index

CT. The cache tag

Set index 0 1234567 Line 0 Tag Valid Byte 0 Byte 1 Byte 2 Byte 3 09 1 86 30 3F 10 45 1 60 4F E0 23 EB 0 06 C7 71 1 91 1 46 0 0 1 - 06 A0 - 2-way set associative cache 78 DE B7 - 07 18 26 C5 4B 2D Line 1 Tag Valid Byte 0 Byte 1 Byte 2 Byte 3 00 0 38 1 OB 0 32 05 6E FO 0 DE 1 1 1 00 - 12 40 - 12 BC 08 67 CO OB 7B C2 88 37 AD 3B 37

Step by Step Solution

3.41 Rating (151 Votes )

There are 3 Steps involved in it

Cache Configuration Cache is twoway set associative E 2 Block size is 4 bytes B 4 Cache has eight se... View full answer

Get step-by-step solutions from verified subject matter experts