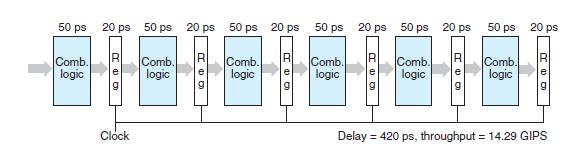

Question: Suppose we could take the system of Figure 4.32 and divide it into an arbitrary number of pipeline stages k, each having a delay of

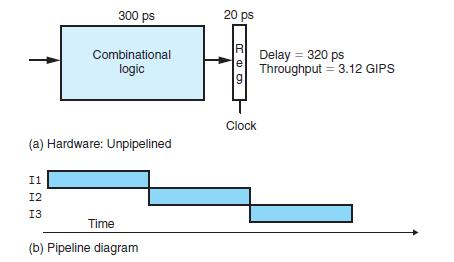

Suppose we could take the system of Figure 4.32 and divide it into an arbitrary number of pipeline stages k, each having a delay of 300/k, and with each pipeline register having a delay of 20 ps.

A. What would be the latency and the throughput of the system, as functions of k?

B. What would be the ultimate limit on the throughput?

Figure 4.32

50 ps Comb. logic 20 ps 50 ps 20 ps 50 ps 20 ps 50 ps 20 ps 50 ps 20 ps Clock Comb. logic Comb. logic Comb. logic Comb. logic 50 ps 20 ps Comb. logic Delay = 420 ps, throughput = 14.29 GIPS

Step by Step Solution

3.31 Rating (163 Votes )

There are 3 Steps involved in it

Each stage would have combinational logic requiring ... View full answer

Get step-by-step solutions from verified subject matter experts