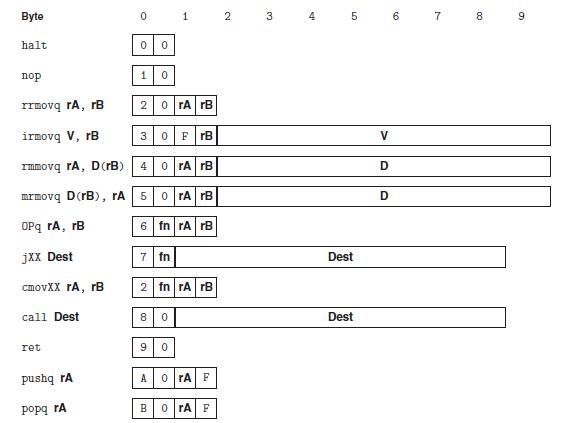

Question: We can see by the instruction encodings (Figures 4.2 and 4.3) that the rrmovq instruction is the unconditional version of a more general class of

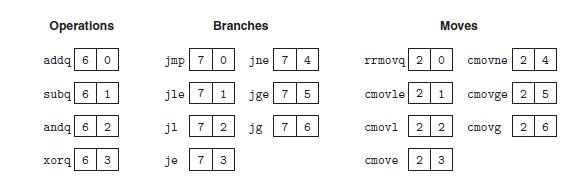

We can see by the instruction encodings (Figures 4.2 and 4.3) that the rrmovq instruction is the unconditional version of a more general class of instructions that include the conditional moves. Show how you would modify the steps for the rrmovq instruction below to also handle the six conditional move instructions. You may find it useful to see how the implementation of the jXX instructions (Figure 4.21) handles conditional behavior.

![Stage Fetch Decode Execute Memory Write back PC update cmovXX rA, rB + icode: ifun M [PC] rA:rB M[PC + 1]](https://dsd5zvtm8ll6.cloudfront.net/images/question_images/1698/2/1/0/0936538a12d7b4bf1698210092483.jpg)

Figures 4.2

Figures 4.3

Figures 4.21

![Stage Fetch Decode Execute Memory Write back PC update JXX Dest icode: ifun M[PC] valC+ Mg[PC + 1] valp PC](https://dsd5zvtm8ll6.cloudfront.net/images/question_images/1698/2/1/0/0626538a10ed23301698210061865.jpg)

Stage Fetch Decode Execute Memory Write back PC update cmovXX rA, rB + icode: ifun M [PC] rA:rB M[PC + 1] PC+2 valp valA valE - R[RA] 0+ valA R[rB] valE PC- valp

Step by Step Solution

3.44 Rating (157 Votes )

There are 3 Steps involved in it

Implementing conditional moves requires only minor changes from regist... View full answer

Get step-by-step solutions from verified subject matter experts