Question: Examples 7.9 and 7.10 point out that the pipelined MIPS processor performance might be better if branches take place during the Execute stage rather than

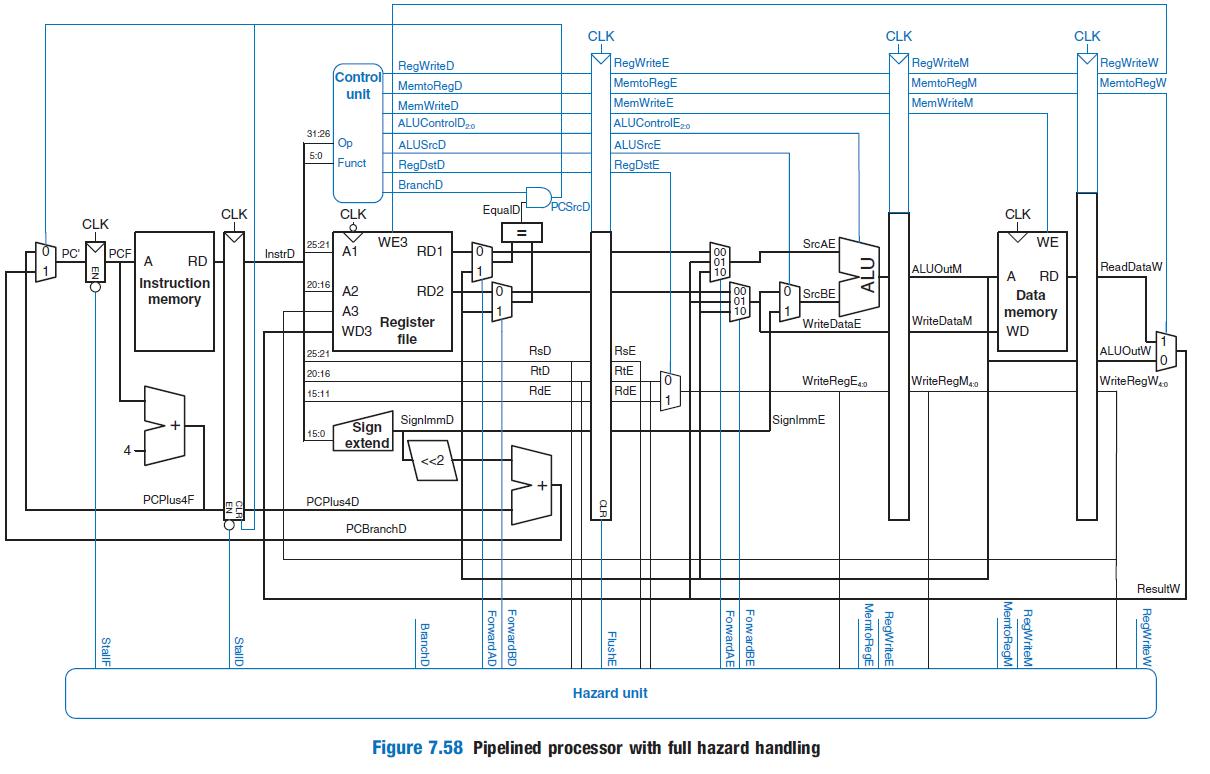

Examples 7.9 and 7.10 point out that the pipelined MIPS processor performance might be better if branches take place during the Execute stage rather than the Decode stage. Show how to modify the pipelined processor from Figure 7.58 to branch in the Execute stage. How do the stall and flush signals change? Redo Examples 7.9 and 7.10 to find the new CPI, cycle time, and overall time to execute the program.

CLK CLK CLK MRegWriteE MemtoRegE MemWriteE ALUControlE20 MRegWriteM MemtoRegM MemWriteM MRegWriteW MemtoRegW RegWriteD Control MemtoRegD unit MemWriteD ALUControlD20 31:26 Op ALUSrcD ALUSrcE 5:0 Funct RegDstD RegDstE BranchD EqualD PCSrcD CLK CLK CLK CLK 25:21 A1 WE3 WE STCAE PC' PCF A InstrD RD1 RD ALUOUTM ReadDataW 10 A RD Instruction 20:16 A2 0SrcBE RD2 Data memory 01 10 memory Register WriteDataE WriteDataM WD3 WD file RsD RSE ALUOutW 25:21 RtD RtE 20:16 WriteRegE WriteRegMao WriteRegW 15:11 RdE RdE SignimmD SignimmE Slgn extend 15:0 <

Step by Step Solution

3.49 Rating (156 Votes )

There are 3 Steps involved in it

The Hazard Unit must no longer produce the ForwardAD and ForwardBD signals PCPlus4 must also be pass... View full answer

Get step-by-step solutions from verified subject matter experts