Design a sum-of-products circuit for segment 5 of the full seven-segment decoder described in Exercise 6.14. Data

Question:

Design a sum-of-products circuit for segment 5 of the full seven-segment decoder described in Exercise 6.14.

Data in Exercise 6.14.

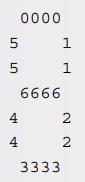

This and following exercises (6.14 – 6.41) share the description of a seven-segment decoder, a combinational circuit with a four-bit input a and a seven-bit output q. Each bit of q corresponds to one of the seven segments of a display according to the following pattern:

That is, bit 0 (the LSB) of q controls the top segment, bit 1 the upper right segment, and so on, with bit 6 (the MSB) controlling the middle segment. Seven-segment decoders are described in more detail in Section 7.3. A full decoder decodes all 16 input combinations – approximating the letters A–F (capital A, C, E, F and lowercase b, d) for combinations 10–15. A decimal decoder decodes only combinations 0–9, the remainder are don’t cares.

Design a sum-of-products circuit for segment 0 of a full seven-segment decoder.

Step by Step Answer:

Digital Design Using VHDL A Systems Approach

ISBN: 9781107098862

1st Edition

Authors: William J. Dally, R. Curtis Harting, Tor M. Aamodt