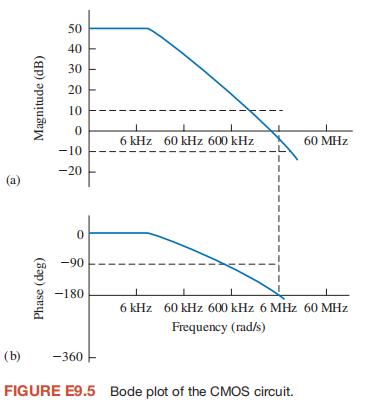

Question: E9.5 An integrated CMOS digital circuit can be repre sented by the Bode plot shown in Figure E9.5. (a) Find the gain and phase margins

E9.5 An integrated CMOS digital circuit can be repre

sented by the Bode plot shown in Figure E9.5.

(a) Find the gain and phase margins of the circuit.

(b) Estimate how much we would need to reduce the system gain (dB) to obtain a phase margin of P M. . = 60°.

(a) Phase (deg) Magnitude (dB) 50 40 30 20 10 -10 -20 0 -90 -180 (b) -360 0 6 kHz 60 kHz 600 kHz 60 MHz 6 kHz 60 kHz 600 kHz 6 MHz 60 MHz Frequency (rad/s) FIGURE E9.5 Bode plot of the CMOS circuit.

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts