Using behavioral VHDL, design a Moore-type finite state machine that detects input test vector that contains the

Fantastic news! We've Found the answer you've been seeking!

Question:

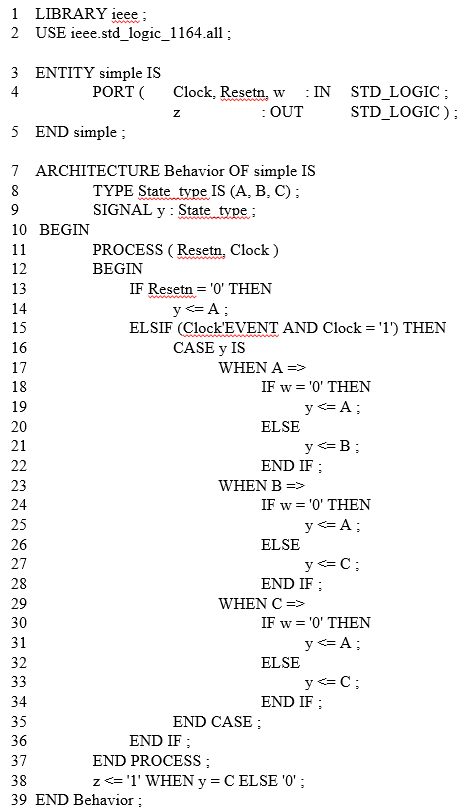

Using behavioral VHDL, design a Moore-type finite state machine that detects input test vector that contains the sequence of ?10?. If the sequence ?10? is detected, the output Z should go high. The input is to be named W, the output is to be named Z, a Clock input is to be used and an active low reset signal (Resetn) should asynchronously reset the machine.

(a) Draw the Moore-type model state diagram for the FSM.

(b) Write the VHDL code to implement the FSM.

We were given code to alter to fit the above question. Please explain the changes for my understanding.

Related Book For

Discrete and Combinatorial Mathematics An Applied Introduction

ISBN: 978-0201726343

5th edition

Authors: Ralph P. Grimaldi

Posted Date: