Question

1. [10 points] Suppose each stage of the instruction takes the following times: IF (Instruction Fetch) = 7 ns, ID (Instruction Decode) = 8

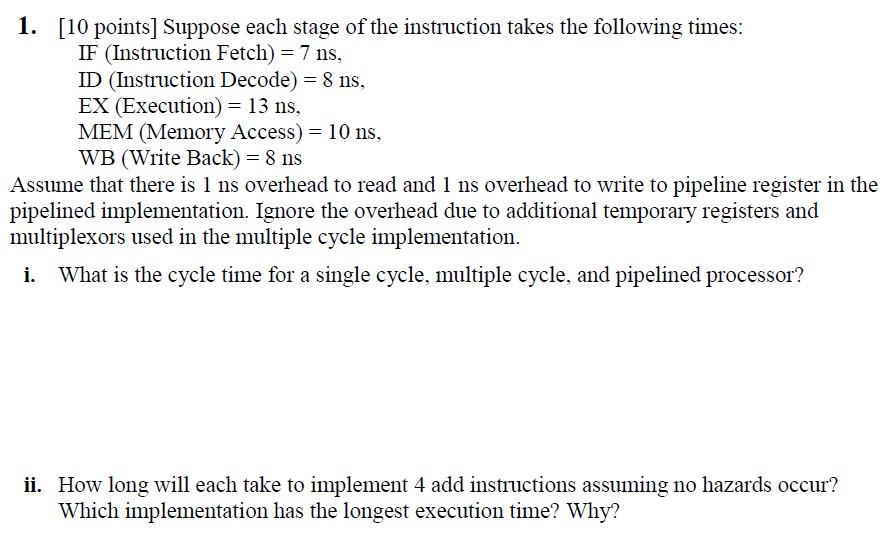

1. [10 points] Suppose each stage of the instruction takes the following times: IF (Instruction Fetch) = 7 ns, ID (Instruction Decode) = 8 ns, EX (Execution) = 13 ns, MEM (Memory Access) = 10 ns, WB (Write Back) = 8 ns Assume that there is 1 ns overhead to read and 1 ns overhead to write to pipeline register in the pipelined implementation. Ignore the overhead due to additional temporary registers and multiplexors used in the multiple cycle implementation. i. What is the cycle time for a single cycle, multiple cycle, and pipelined processor? ii. How long will each take to implement 4 add instructions assuming no hazards occur? Which implementation has the longest execution time? Why?

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get StartedRecommended Textbook for

Computer Organization And Design The Hardware Software Interface

Authors: David A. Patterson, John L. Hennessy

4th Revised Edition

0123747503, 978-0123747501

Students also viewed these Programming questions

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

View Answer in SolutionInn App