Answered step by step

Verified Expert Solution

Question

1 Approved Answer

1 . 2 Complete the timeline of the program assuming that you have an always - taken branch predictor. Assume that the branch prediction happens

Complete the timeline of the program assuming that you have an alwaystaken branch predictor. Assume that the branch prediction happens

within the ID stage, and the full branch outcome is available in the EX stage. For conciseness, use FDEMW for IFIDEXMEMWB stages in the

table. Also use N for NOP. In empty rows, add proper instructions from the assembly program and complete the table. Show mispredicted

instructions as well in the table; you need to invalidate those instructions at the right time. ptsConsider the code snippet given below:

addi x x

addi x x

addi x x

LOOP:

lw xx

lw xx

add x x x

add x x x

addi x x

addi x x

blt x x LOOP

Abbreviations

IF: Instruction fetch stage

ID: Instruction decode register file read stage

EX: execution

MEM: Data memory access

WB: Write back to the register file

NOP: No operation; a bubble

Key assumptions

The writeback data in the WB stage is available in the decode stage at the same cycle.

The processor has forwarding links for data hazard resolution EX ID and MEM ID

Forwarded data from the executionmemory stage is visible to the decode stage at the same cycle ie if an instruction receives a forwarded data from EXMEM stage, align the ID stage of the next instruction with the EXMEM stage of the previous instruction

The processor has a branch predictor each problem will specify which predictor we have and a branch target buffer BTB

We need to compute the full branch outcome at least once to have the target address in the branch target buffer.

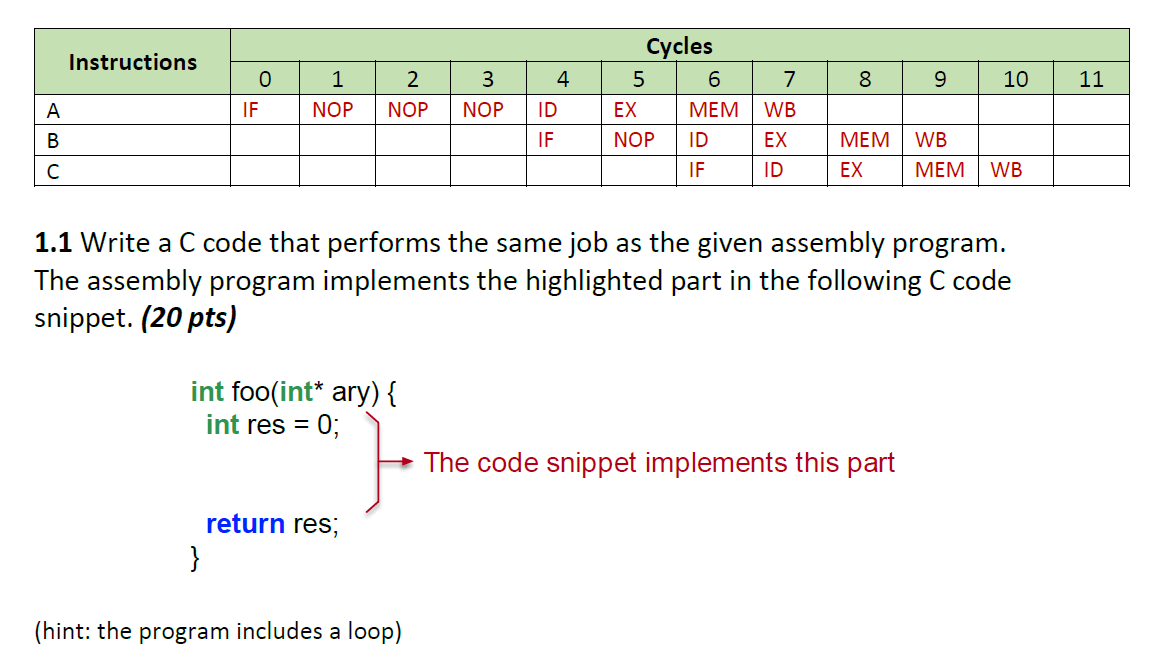

When "NOP" exists in a pipeline stage, the next instruction cannot complete the previous stage. For example, in the timeline given below, instruction B cannot start IF until the NOP in ID stage of instruction A is removed. Likewise, Instruction C needs to wait until the NOP in the ID stage caused by instruction B is removed thats why IF for instruction C started at cycle not

Write a code that performs the same job as the given assembly program.

The assembly program implements the highlighted part in the following code

snippet. pts

hint: the program includes a loop

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started