Answered step by step

Verified Expert Solution

Question

1 Approved Answer

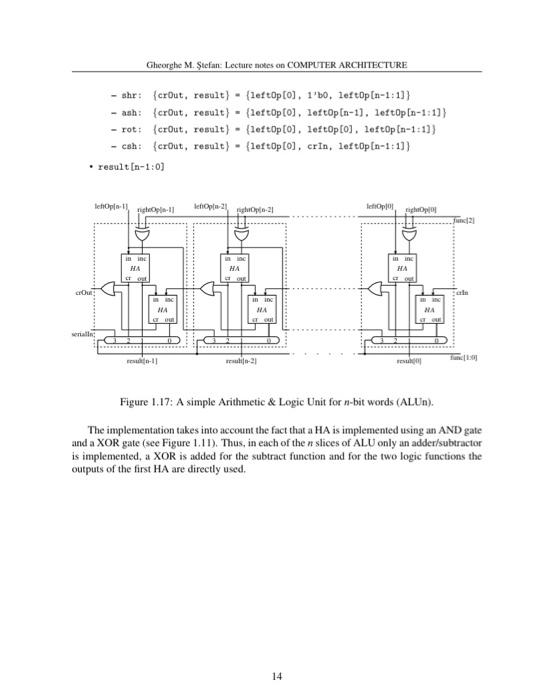

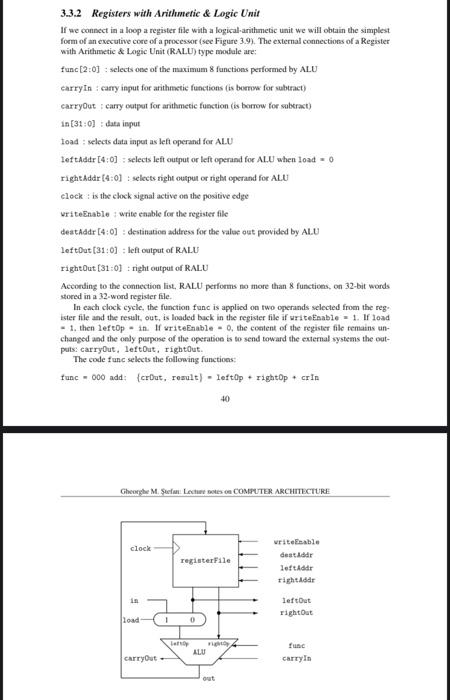

1) Adapt the previously defined ALU in Figure 1.17 to the set of function just defined in 3.3.2 Registers with Arithmetic & Logic Unit. 2)

1) Adapt the previously defined ALU in Figure 1.17 to the set of function just defined in 3.3.2 Registers with Arithmetic & Logic Unit.

2) For the RALU unit defined in 3.3.2 Registers with Arithmetic & Logic Unit design the sequence of commands, like in Table 3.2, which perform the following sequence of operations: load two numbers (17 and 4) in register file, subtract them, multiply the result by 4, add with 44, divide by 2, and send out the result on the left output.

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started