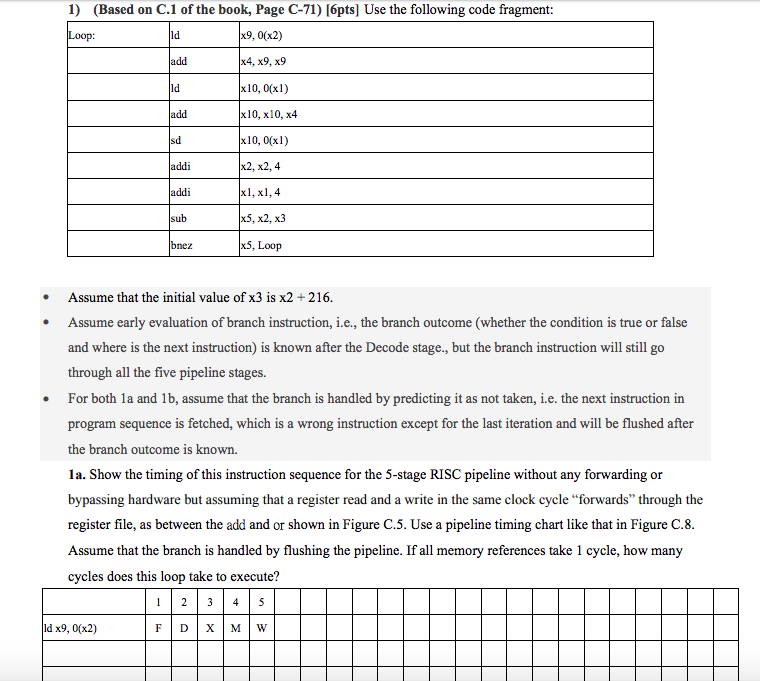

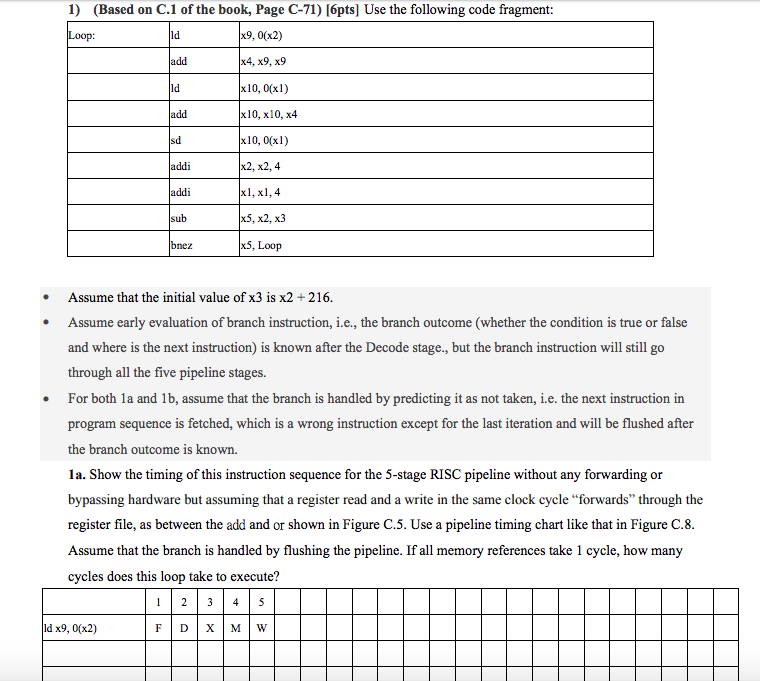

1) (Based on C.1 of the book, Page C-71) [6pts) Use the following code fragment: Loop: |x9, 0(x2) x4, x9,x9 X10, 0(x1) x10, x10, x4 x10, 0(xl) x2, x2,4 addi |xl, xl, 4 x5, x2, x3 sub brez x5, Loop Assume that the initial value of x3 is x2 + 216. Assume early evaluation of branch instruction, i.e., the branch outcome (whether the condition is true or false and where is the next instruction) is known after the Decode stage., but the branch instruction will still go through all the five pipeline stages. For both la and 1b, assume that the branch is handled by predicting it as not taken, i.e. the next instruction in program sequence is fetched, which is a wrong instruction except for the last iteration and will be flushed after the branch outcome is known. 1a. Show the timing of this instruction sequence for the 5-stage RISC pipeline without any forwarding or bypassing hardware but assuming that a register read and a write in the same clock cycle "forwards through the register file, as between the add and or shown in Figure C.5. Use a pipeline timing chart like that in Figure C.8. Assume that the branch is handled by flushing the pipeline. If all memory references take 1 cycle, how many cycles does this loop take to execute? ld x9, 0(x2) FDXMW 1) (Based on C.1 of the book, Page C-71) [6pts) Use the following code fragment: Loop: |x9, 0(x2) x4, x9,x9 X10, 0(x1) x10, x10, x4 x10, 0(xl) x2, x2,4 addi |xl, xl, 4 x5, x2, x3 sub brez x5, Loop Assume that the initial value of x3 is x2 + 216. Assume early evaluation of branch instruction, i.e., the branch outcome (whether the condition is true or false and where is the next instruction) is known after the Decode stage., but the branch instruction will still go through all the five pipeline stages. For both la and 1b, assume that the branch is handled by predicting it as not taken, i.e. the next instruction in program sequence is fetched, which is a wrong instruction except for the last iteration and will be flushed after the branch outcome is known. 1a. Show the timing of this instruction sequence for the 5-stage RISC pipeline without any forwarding or bypassing hardware but assuming that a register read and a write in the same clock cycle "forwards through the register file, as between the add and or shown in Figure C.5. Use a pipeline timing chart like that in Figure C.8. Assume that the branch is handled by flushing the pipeline. If all memory references take 1 cycle, how many cycles does this loop take to execute? ld x9, 0(x2) FDXMW