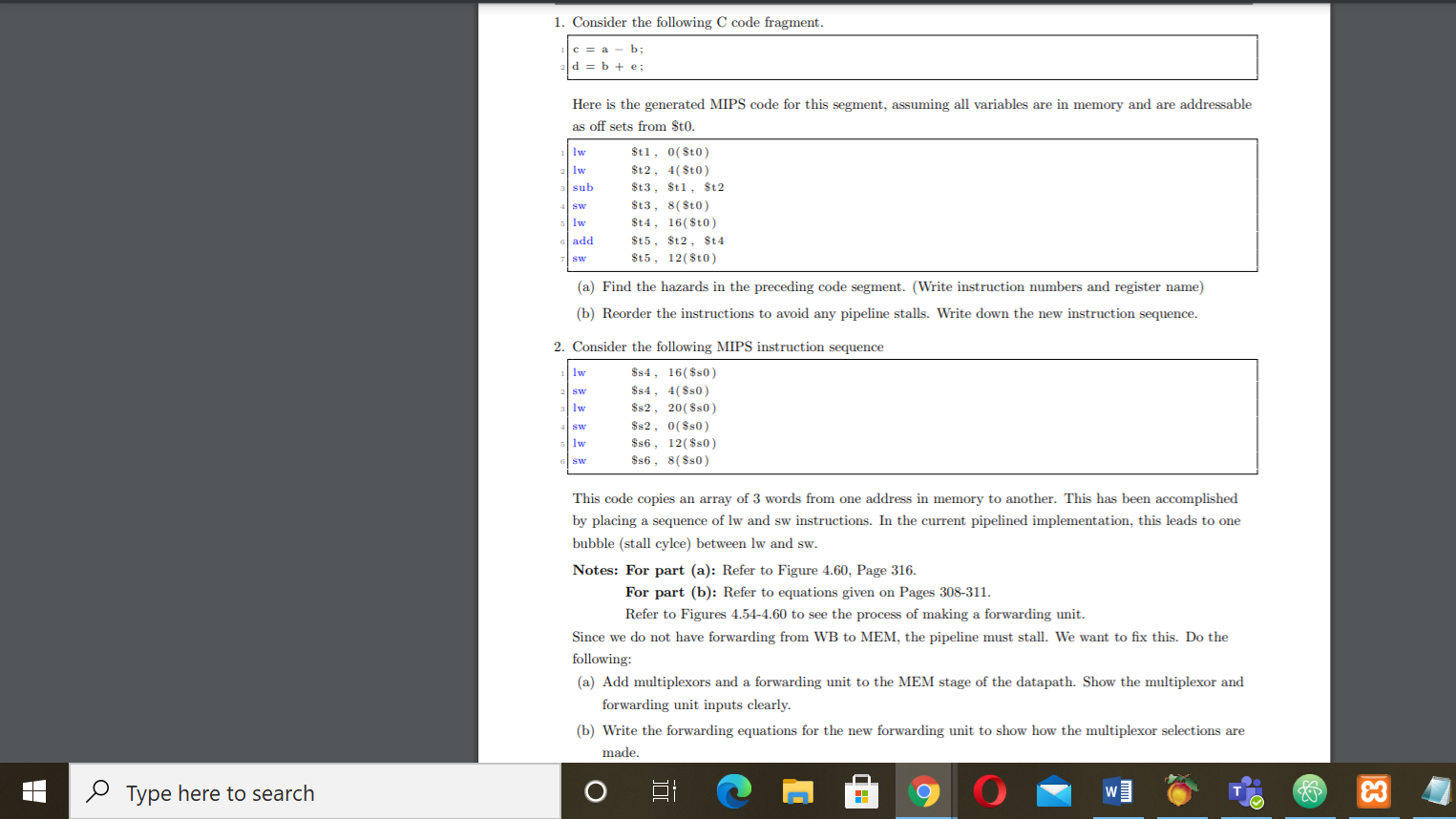

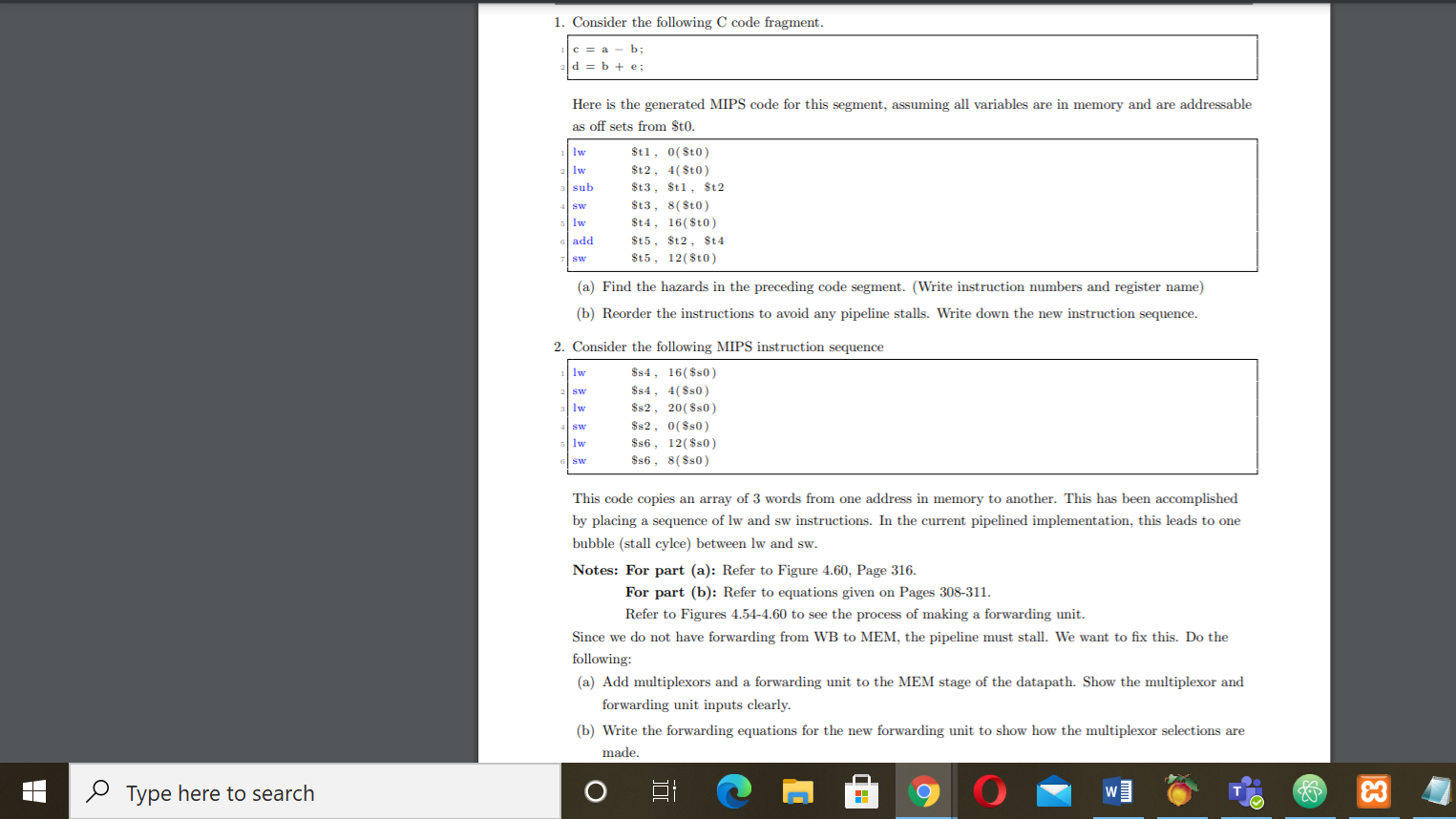

1. Consider the following C code fragment. c = a - b; d = b + e; Here is the generated MIPS code for this segment, assuming all variables are in memory and are addressable as off sets from Sto. lw Iw sub sw lw add $t1, 0(Sto) $t2, 4($t0) $t3, $t1, St2 $t3, 8( $t0) $t4, 16($t0) $t5, $t2, St4 $t5, 12($t0) SW (a) Find the hazards in the preceding code segment. (Write instruction numbers and register name) (b) Reorder the instructions to avoid any pipeline stalls. Write down the new instruction sequence. Iw Sw 2. Consider the following MIPS instruction sequence $s4, 16($sp) $84, 4(80) $s2, 20($so) $82, 0(80) $86, 12( $80) $86, 8(90) lw SW lw SW This code copies an array of 3 words from one address in memory to another. This has been accomplished by placing a sequence of lw and sw instructions. In the current pipelined implementation, this leads to one bubble (stall cylce) between lw and sw. Notes: For part (a): Refer to Figure 4.60, Page 316. For part (b): Refer to equations given on Pages 308-311. Refer to Figures 4.54-4.60 to see the process of making a forwarding unit. Since we do not have forwarding from WB to MEM, the pipeline must stall. We want to fix this. Do the following: (a) Add multiplexors and a forwarding unit to the MEM stage of the datapath. Show the multiplexor and forwarding unit inputs clearly. (b) Write the forwarding equations for the new forwarding unit to show how the multiplexor selections are made. 1 O Type here to search JOI E 3 1. Consider the following C code fragment. c = a - b; d = b + e; Here is the generated MIPS code for this segment, assuming all variables are in memory and are addressable as off sets from Sto. lw Iw sub sw lw add $t1, 0(Sto) $t2, 4($t0) $t3, $t1, St2 $t3, 8( $t0) $t4, 16($t0) $t5, $t2, St4 $t5, 12($t0) SW (a) Find the hazards in the preceding code segment. (Write instruction numbers and register name) (b) Reorder the instructions to avoid any pipeline stalls. Write down the new instruction sequence. Iw Sw 2. Consider the following MIPS instruction sequence $s4, 16($sp) $84, 4(80) $s2, 20($so) $82, 0(80) $86, 12( $80) $86, 8(90) lw SW lw SW This code copies an array of 3 words from one address in memory to another. This has been accomplished by placing a sequence of lw and sw instructions. In the current pipelined implementation, this leads to one bubble (stall cylce) between lw and sw. Notes: For part (a): Refer to Figure 4.60, Page 316. For part (b): Refer to equations given on Pages 308-311. Refer to Figures 4.54-4.60 to see the process of making a forwarding unit. Since we do not have forwarding from WB to MEM, the pipeline must stall. We want to fix this. Do the following: (a) Add multiplexors and a forwarding unit to the MEM stage of the datapath. Show the multiplexor and forwarding unit inputs clearly. (b) Write the forwarding equations for the new forwarding unit to show how the multiplexor selections are made. 1 O Type here to search JOI E 3