Question

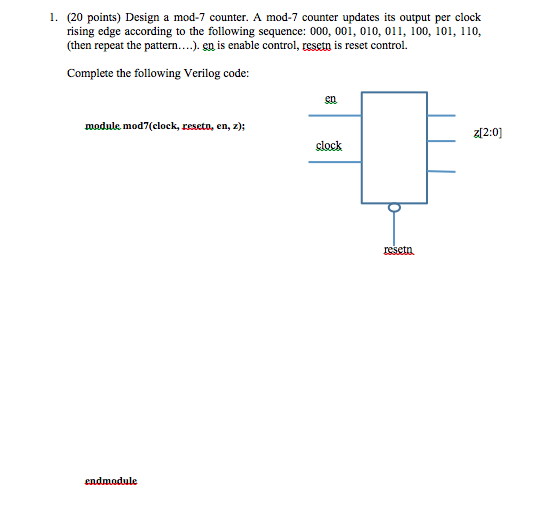

1. (20 points) Design a mod-7 counter. A mod-7 counter updates its output per clock rising edge according to the following sequence: 000, 001,

1. (20 points) Design a mod-7 counter. A mod-7 counter updates its output per clock rising edge according to the following sequence: 000, 001, 010, 011, 100, 101, 110, (then repeat the pattern....). en is enable control, resetn is reset control. Complete the following Verilog code: module mod7(clock, reseto, en, z); endmodule en clock resetn z[2:0]

Step by Step Solution

3.40 Rating (150 Votes )

There are 3 Steps involved in it

Step: 1

module input mod 1 clock always begin ...

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get StartedRecommended Textbook for

A Balanced Introduction to Computer Science

Authors: David Reed

3rd edition

132166755, 978-0132166751

Students also viewed these Electrical Engineering questions

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

View Answer in SolutionInn App