Question

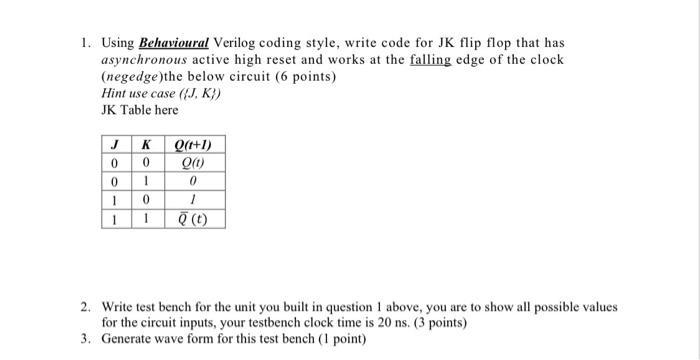

1. Using Behavioural Verilog coding style, write code for JK flip flop that has asynchronous active high reset and works at the falling edge

1. Using Behavioural Verilog coding style, write code for JK flip flop that has asynchronous active high reset and works at the falling edge of the clock (negedge)the below circuit (6 points) Hint use case (J. K}) JK Table here JK Q(t+1) Q(1) 0 1 Q (t) 0 0 1 1 0 I 0 1 2. Write test bench for the unit you built in question 1 above, you are to show all possible values for the circuit inputs, your testbench clock time is 20 ns. (3 points) 3. Generate wave form for this test bench (1 point)

Step by Step Solution

There are 3 Steps involved in it

Step: 1

1 Behavioral Verilog Code for JK FlipFlo...

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get StartedRecommended Textbook for

Fundamentals of Digital Logic and Microcontrollers

Authors: M. Rafiquzzaman

6th edition

1-118-85579-9, 1118855795, 9781118969304, 978-1118855799

Students also viewed these Programming questions

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

View Answer in SolutionInn App