Question

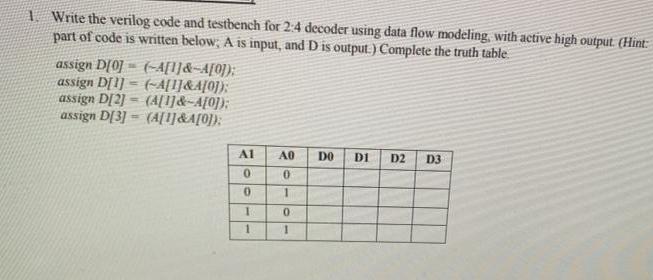

1. Write the verilog code and testbench for 2:4 decoder using data flow modeling, with active high output. (Hint: part of code is written

1. Write the verilog code and testbench for 2:4 decoder using data flow modeling, with active high output. (Hint: part of code is written below; A is input, and D is output.) Complete the truth table. (-A[1]&-A[0]); assign D[0] assign D[1] (-A[1]&A[0]); assign D[2] (A[1]&-A[0]); assign D[3] (A[1]&A[0]); T A1 A0 DO D1 D2 D3 0 1 00 1 1 la 0 1

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Based on the provided Verilog code for a 2to4 decoder we can fill out the given truth table A decode...

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get StartedRecommended Textbook for

Income Tax Fundamentals 2013

Authors: Gerald E. Whittenburg, Martha Altus Buller, Steven L Gill

31st Edition

1111972516, 978-1285586618, 1285586611, 978-1285613109, 978-1111972516

Students also viewed these Programming questions

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

View Answer in SolutionInn App