Answered step by step

Verified Expert Solution

Question

1 Approved Answer

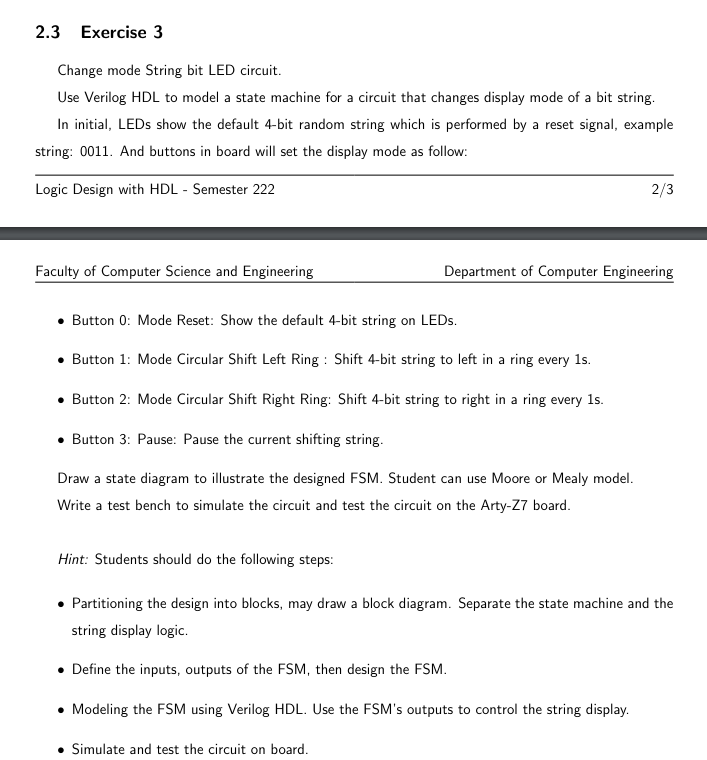

2 . 3 Exercise 3 Change mode String bit LED circuit. Use Verilog HDL to model a state machine for a circuit that changes display

Exercise

Change mode String bit LED circuit.

Use Verilog HDL to model a state machine for a circuit that changes display mode of a bit string.

In initial, LEDs show the default bit random string which is performed by a reset signal, example

string: And buttons in board will set the display mode as follow:

Logic Design with HDL Semester

Faculty of Computer Science and Engineering Department of Computer Engineering

Button : Mode Reset: Show the default bit string on LEDs.

Button : Mode Circular Shift Left Ring : Shift bit string to left in a ring every s

Button : Mode Circular Shift Right Ring: Shift bit string to right in a ring every s

Button : Pause: Pause the current shifting string.

Draw a state diagram to illustrate the designed FSM Student can use Moore or Mealy model.

Write a test bench to simulate the circuit and test the circuit on the ArtyZ board.

Hint: Students should do the following steps:

Partitioning the design into blocks, may draw a block diagram. Separate the state machine and the

string display logic.

Define the inputs, outputs of the FSM then design the FSM

Modeling the FSM using Verilog HDL Use the FSMs outputs to control the string display.

Simulate and test the circuit on board. Exercise

Change mode String bit LED circuit.

Use Verilog HDL to model a state machine for a circuit that changes display mode of a bit string.

In initial, LEDs show the default bit random string which is performed by a reset signal, example

string: And buttons in board will set the display mode as follow:

Logic Design with HDL Semester

Button : Mode Reset: Show the default bit string on LEDs.

Button : Mode Circular Shift Left Ring : Shift bit string to left in a ring every s

Button : Mode Circular Shift Right Ring: Shift bit string to right in a ring every s

Button : Pause: Pause the current shifting string.

Draw a state diagram to illustrate the designed FSM Student can use Moore or Mealy model.

Write a test bench to simulate the circuit and test the circuit on the ArtyZ board.

Hint: Students should do the following steps:

Partitioning the design into blocks, may draw a block diagram. Separate the state machine and the

string display logic.

Define the inputs, outputs of the FSM then design the FSM

Modeling the FSM using Verilog HDL Use the FSMs outputs to control the string display.

Simulate and test the circuit on board. Cho toi code verilog va tebench

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started