Answered step by step

Verified Expert Solution

Question

1 Approved Answer

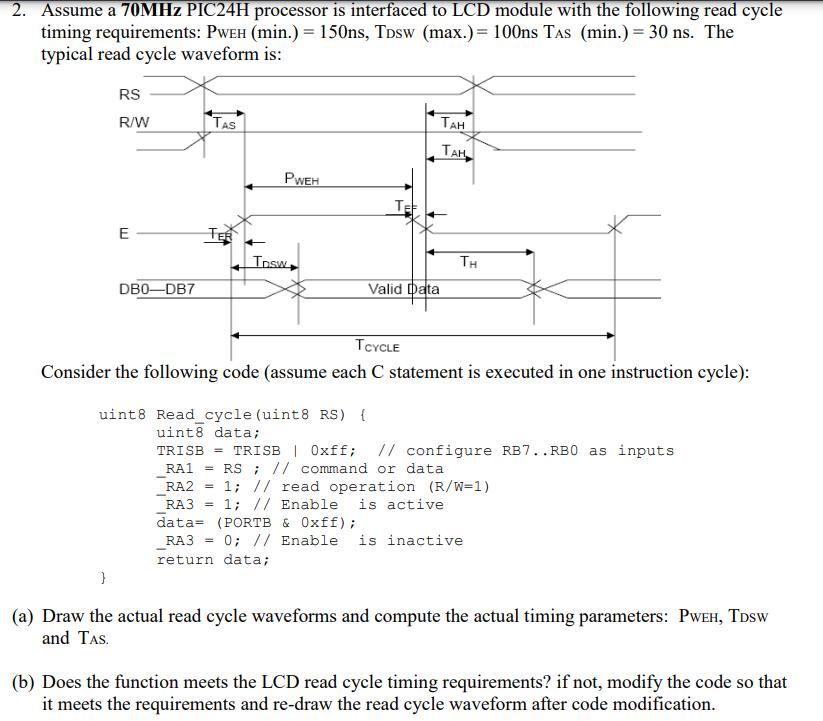

2. Assume a 70MHz PIC24H processor is interfaced to LCD module with the following read cycle timing requirements: PWEH (min.) = 150ns, TDsw (max.)

2. Assume a 70MHz PIC24H processor is interfaced to LCD module with the following read cycle timing requirements: PWEH (min.) = 150ns, TDsw (max.) = 100ns TAS (min.) = 30 ns. The typical read cycle waveform is: RS R/W TAH TAS TAH PWEH E TER Ipsw TH DB0-DB7 Valid Data TCYCLE Consider the following code (assume each C statement is executed in one instruction cycle): uint8 Read_cycle (uint8 RS) { uint8 data; TRISB = TRISB 0xff; // configure RB7..RB0 as inputs. RA1 RS; // command or data RA2 = 1; // read operation (R/W=1) RA3 = 1; // Enable is active data (PORTB & 0xff); RA3 = 0; // Enable is inactive return data; } (a) Draw the actual read cycle waveforms and compute the actual timing parameters: PWEH, TDSW and TAS. (b) Does the function meets the LCD read cycle timing requirements? if not, modify the code so that it meets the requirements and re-draw the read cycle waveform after code modification.

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started