Answered step by step

Verified Expert Solution

Question

1 Approved Answer

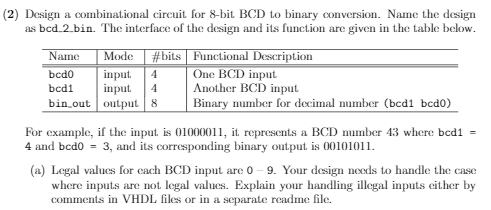

(2) Design a combinational circuit for 8-bit BCD to binary conversion. Name the design as bed. 2.bin. The interface of the design and its function

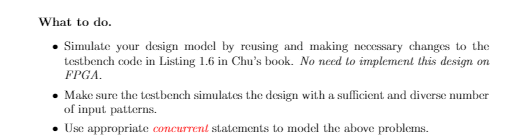

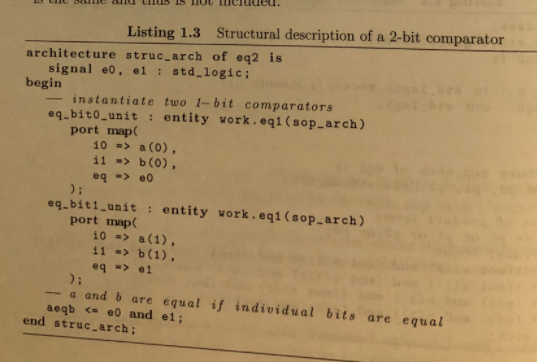

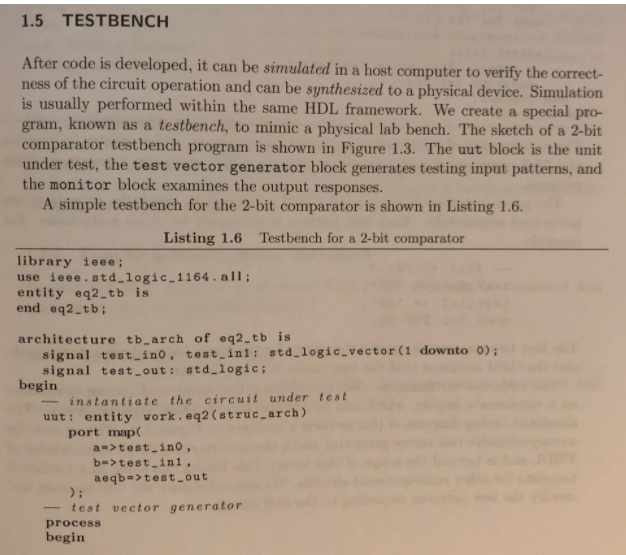

(2) Design a combinational circuit for 8-bit BCD to binary conversion. Name the design as bed. 2.bin. The interface of the design and its function are given in the table below. Name Mode #bits Functional Description bodo input One BCD input bedi input 4 Another BCD input bin_out output 8 Binary number for decimal number (bcd1 bedo) For example, if the input is 01000011, it represents a BCD number 43 where bed1 = 4 and bedo = 3, and its corresponding binary output is 00101011. (a) Legal values for each BCD input are 0 - 9. Your design needs to handle the case where inputs are not legal values. Explain your handling illegal inputs either by comments in VHDL files or in a separate readme file. What to do. Simulate your design model by reusing and making necessary changes to the testbench code in Listing 1.6 in Chu's book. No need to implement this design on FPGA. . Make sure the testbench simulates the design with a sufficient and diverse number of input patterns. Use appropriate concurrent statements to model the above problems. 1.2.6 Code of a 2-bit comparator We can expand the comparator to 2-bit inputs. Let the input be a and b and the output be aeqb. The aeqb signal is asserted when both bits of a and b are equal. The code is shown in Listing 1.2. Listing 1.2 Gate-level implementation of a 2-bit comparator library ieee; use ieee.std_logic_1164. all; entity eq2 is port a, b: in std_logic_vector (1 downto 0); aeqb : out std_logic end eq2; architecture sop-arch of eq2 is signal po, pi, P2, P3: std_logic; begin sum of product terms aeqb a(0) 11 => (0), eq => 0 eq-biti unit : entity work.eqi (sop-arch) port map 10 => a(1) 11 -> b(1), eq => 1 - a and b are equal if individual bits are equal aeqb test_ino, br>test_ini, aeqb=>test_out test vector generator process begin (2) Design a combinational circuit for 8-bit BCD to binary conversion. Name the design as bed. 2.bin. The interface of the design and its function are given in the table below. Name Mode #bits Functional Description bodo input One BCD input bedi input 4 Another BCD input bin_out output 8 Binary number for decimal number (bcd1 bedo) For example, if the input is 01000011, it represents a BCD number 43 where bed1 = 4 and bedo = 3, and its corresponding binary output is 00101011. (a) Legal values for each BCD input are 0 - 9. Your design needs to handle the case where inputs are not legal values. Explain your handling illegal inputs either by comments in VHDL files or in a separate readme file. What to do. Simulate your design model by reusing and making necessary changes to the testbench code in Listing 1.6 in Chu's book. No need to implement this design on FPGA. . Make sure the testbench simulates the design with a sufficient and diverse number of input patterns. Use appropriate concurrent statements to model the above problems. 1.2.6 Code of a 2-bit comparator We can expand the comparator to 2-bit inputs. Let the input be a and b and the output be aeqb. The aeqb signal is asserted when both bits of a and b are equal. The code is shown in Listing 1.2. Listing 1.2 Gate-level implementation of a 2-bit comparator library ieee; use ieee.std_logic_1164. all; entity eq2 is port a, b: in std_logic_vector (1 downto 0); aeqb : out std_logic end eq2; architecture sop-arch of eq2 is signal po, pi, P2, P3: std_logic; begin sum of product terms aeqb a(0) 11 => (0), eq => 0 eq-biti unit : entity work.eqi (sop-arch) port map 10 => a(1) 11 -> b(1), eq => 1 - a and b are equal if individual bits are equal aeqb test_ino, br>test_ini, aeqb=>test_out test vector generator process begin

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started