Answered step by step

Verified Expert Solution

Question

1 Approved Answer

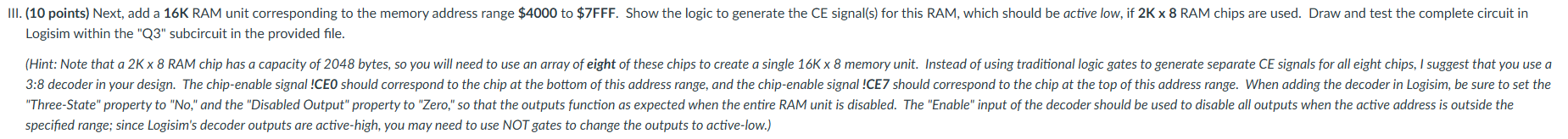

3 ) ( 1 0 points ) Next, add a 1 6 K RAM unit corresponding to the memory address range $ 4 0 0

points Next, add a K RAM unit corresponding to the memory address range $ to $FFF Show the logic to generate the CE signals for this RAM, which should be active low, if K x RAM chips are used. Draw and test the complete circuit in Logisim within the Q subcircuit in the provided file.

Hint: Note that a K x RAM chip has a capacity of bytes, so you will need to use an array of eight of these chips to create a single K x memory unit. Instead of using traditional logic gates to generate separate CE signals for all eight chips, I suggest that you use a : decoder in your design. The chipenable signal CE should correspond to the chip at the bottom of this address range, and the chipenable signal CE should correspond to the chip at the top of this address range. When adding the decoder in Logisim, be sure to set the "ThreeState" property to No and the "Disabled Output" property to "Zero," so that the outputs function as expected when the entire RAM unit is disabled. The "Enable" input of the decoder should be used to disable all outputs when the active address is outside the specified range; since Logisim's decoder outputs are activehigh, you may need to use NOT gates to change the outputs to activelow.

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started