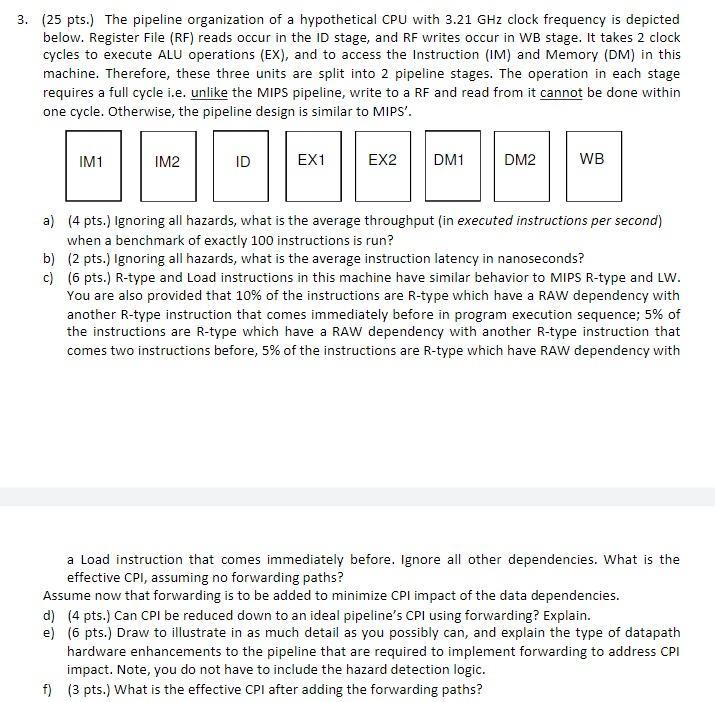

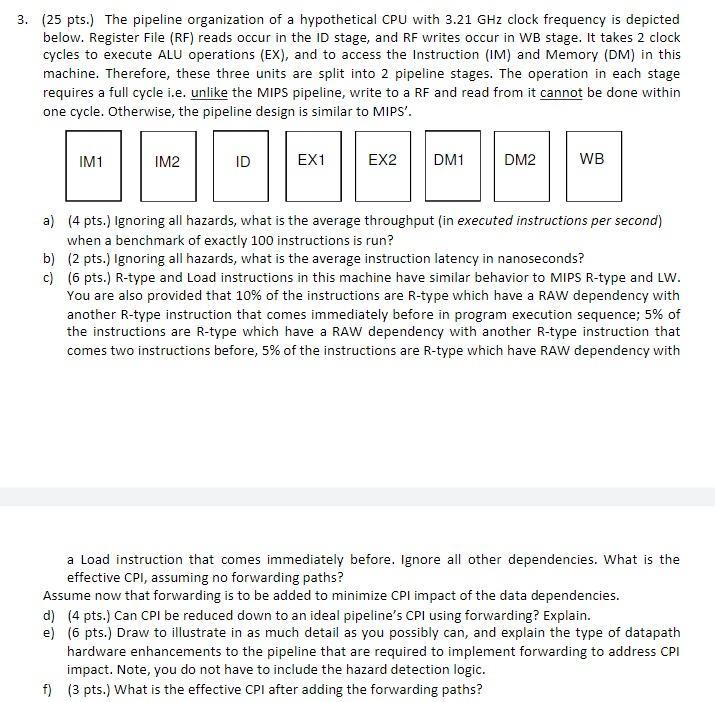

3. (25 pts.) The pipeline organization of a hypothetical CPU with 3.21 GHz clock frequency is depicted below. Register File (RF) reads occur in the ID stage, and RF writes occur in WB stage. It takes 2 clock cycles to execute ALU operations (EX), and to access the Instruction (IM) and Memory (DM) in this machine. Therefore, these three units are split into 2 pipeline stages. The operation in each stage requires a full cycle i.e. unlike the MIPS pipeline, write to a RF and read from it cannot be done within one cycle. Otherwise, the pipeline design is similar to MIPS'. IM1 IM2 ID EX1 EX2 DM1 DM2 WB a) (4 pts.) Ignoring all hazards, what is the average throughput (in executed instructions per second) when a benchmark of exactly 100 instructions is run? b) (2 pts.) Ignoring all hazards, what is the average instruction latency in nanoseconds? c) (6 pts.) R-type and Load instructions in this machine have similar behavior to MIPS R-type and LW. You are also provided that 10% of the instructions are R-type which have a RAW dependency with another R-type instruction that comes immediately before in program execution sequence; 5% of the instructions are R-type which have a RAW dependency with another R-type instruction that comes two instructions before, 5% of the instructions are R-type which have RAW dependency with a Load instruction that comes immediately before. Ignore all other dependencies. What is the effective CPI, assuming no forwarding paths? Assume now that forwarding is to be added to minimize CPI impact of the data dependencies. d) (4 pts.) Can CPI be reduced down to an ideal pipeline's CPI using forwarding? Explain. e) (6 pts.) Draw to illustrate in as much detail as you possibly can, and explain the type of datapath hardware enhancements to the pipeline that are required to implement forwarding to address CPI impact. Note, you do not have to include the hazard detection logic. f) (3 pts.) What is the effective CPI after adding the forwarding paths? 3. (25 pts.) The pipeline organization of a hypothetical CPU with 3.21 GHz clock frequency is depicted below. Register File (RF) reads occur in the ID stage, and RF writes occur in WB stage. It takes 2 clock cycles to execute ALU operations (EX), and to access the Instruction (IM) and Memory (DM) in this machine. Therefore, these three units are split into 2 pipeline stages. The operation in each stage requires a full cycle i.e. unlike the MIPS pipeline, write to a RF and read from it cannot be done within one cycle. Otherwise, the pipeline design is similar to MIPS'. IM1 IM2 ID EX1 EX2 DM1 DM2 WB a) (4 pts.) Ignoring all hazards, what is the average throughput (in executed instructions per second) when a benchmark of exactly 100 instructions is run? b) (2 pts.) Ignoring all hazards, what is the average instruction latency in nanoseconds? c) (6 pts.) R-type and Load instructions in this machine have similar behavior to MIPS R-type and LW. You are also provided that 10% of the instructions are R-type which have a RAW dependency with another R-type instruction that comes immediately before in program execution sequence; 5% of the instructions are R-type which have a RAW dependency with another R-type instruction that comes two instructions before, 5% of the instructions are R-type which have RAW dependency with a Load instruction that comes immediately before. Ignore all other dependencies. What is the effective CPI, assuming no forwarding paths? Assume now that forwarding is to be added to minimize CPI impact of the data dependencies. d) (4 pts.) Can CPI be reduced down to an ideal pipeline's CPI using forwarding? Explain. e) (6 pts.) Draw to illustrate in as much detail as you possibly can, and explain the type of datapath hardware enhancements to the pipeline that are required to implement forwarding to address CPI impact. Note, you do not have to include the hazard detection logic. f) (3 pts.) What is the effective CPI after adding the forwarding paths