Question

3. Consider the following loop. LOOP: LDUR X10, [X1, #0] LDUR X11, [X1, #8] ADD X12, X10, X11 SUBI X1, X1, #16 CBNZ X12,

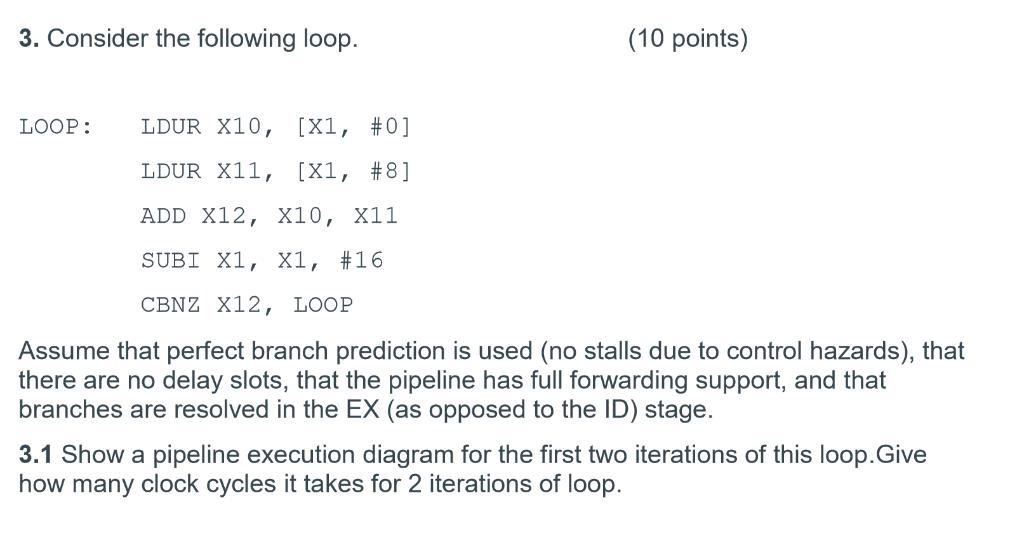

3. Consider the following loop. LOOP: LDUR X10, [X1, #0] LDUR X11, [X1, #8] ADD X12, X10, X11 SUBI X1, X1, #16 CBNZ X12, LOOP (10 points) Assume that perfect branch prediction is used (no stalls due to control hazards), that there are no delay slots, that the pipeline has full forwarding support, and that branches are resolved in the EX (as opposed to the ID) stage. 3.1 Show a pipeline execution diagram for the first two iterations of this loop.Give how many clock cycles it takes for 2 iterations of loop.

Step by Step Solution

3.41 Rating (157 Votes )

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get StartedRecommended Textbook for

Computer Organization and Design The Hardware Software Interface

Authors: David A. Patterson, John L. Hennessy

5th edition

124077269, 978-0124077263

Students also viewed these Programming questions

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

View Answer in SolutionInn App