Question

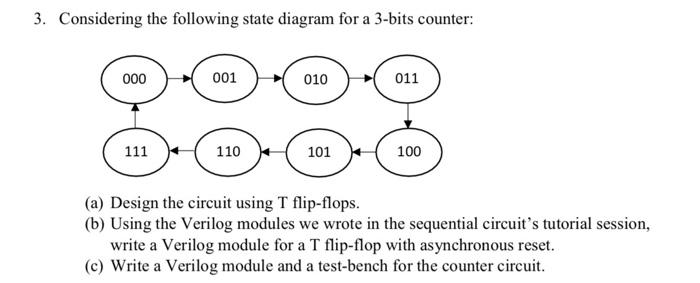

3. Considering the following state diagram for a 3-bits counter: 000 001 010 011 111 110 101 100 (a) Design the circuit using T

3. Considering the following state diagram for a 3-bits counter: 000 001 010 011 111 110 101 100 (a) Design the circuit using T flip-flops. (b) Using the Verilog modules we wrote in the sequential circuit's tutorial session, write a Verilog module for a T flip-flop with asynchronous reset. (c) Write a Verilog module and a test-bench for the counter circuit.

Step by Step Solution

3.37 Rating (150 Votes )

There are 3 Steps involved in it

Step: 1

Sure lets break down each part of your question a Designing the circuit using T flipf...

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get StartedRecommended Textbook for

Design And Analysis Of Experiments

Authors: Douglas C., Montgomery

5th Edition

978-0471316497, 0471316490

Students also viewed these Programming questions

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

View Answer in SolutionInn App