Answered step by step

Verified Expert Solution

Question

1 Approved Answer

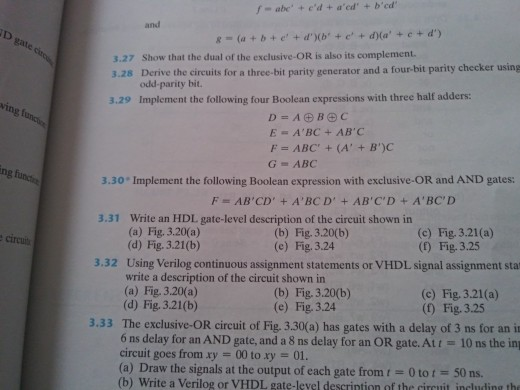

3.29 and D gate ciru ab+ e' + d'xb +e'+ d(a'+e+d') 3.27 Show that the dual of the exclusive-OR is also its complement. 3.28 Derive

3.29

and D gate ciru ab+ e' + d'xb +e'+ d(a'+e+d') 3.27 Show that the dual of the exclusive-OR is also its complement. 3.28 Derive the cireuits for a three-bit parity generator and a four-bit parity checker using odd-parity bit. Implement the following four Boolean expressions with three half adders: G- ABC ng funcia 3.30 Implement the following Boolean expression with exclusive-OR and AND gates: F AB'CD A'BCD' AB'C'D +A'BCD Write an HDL gate-level description of the circuit shown in (a) Fig. 3.20(a) (d) Fig. 3.21(b) 3.31 (c) Fig. 3.21(a) ([) Fig. 3.25 (b) Fig. 3.20(b) (e) Fig. 3.24 3.32 Using Verilog continuous assignment statements or VHDL signal assignment stat (b) Fig. 3.20(b) write a description of the circuit shown in (a) Fig. 3.20(a) (d) Fig. 3.21(b) (c) Fig. 3.21(a) (1) Fig. 3.25 (e) Fig. 3.24 3.33 The exclusive-OR circuit of Fig. 3.30(a) has gates with a delay of 3 ns for an in 6 ns delay for an AND gate, and a 8 ns delay for an OR gate. Att 10 ns the in circuit goes from xy- 00 to xy 01. (a) Draw the signals at the output of each gate from r 0 tot 50 ns (b) Write a Verilog or VHDL gate-level descrintion of the cireuit including theStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started