Question

4. (40 points) Size the following circuit using LE and determine the total delay and size of each gate when Coff-path =0, Coff-path=5, Coff-path

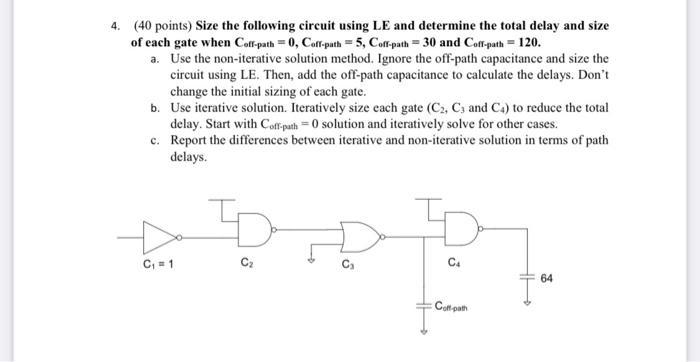

4. (40 points) Size the following circuit using LE and determine the total delay and size of each gate when Coff-path =0, Coff-path=5, Coff-path 30 and Coff-path = 120. a. Use the non-iterative solution method. Ignore the off-path capacitance and size the circuit using LE. Then, add the off-path capacitance to calculate the delays. Don't change the initial sizing of each gate. b. Use iterative solution. Iteratively size each gate (C2, C3 and C4) to reduce the total delay. Start with Coff-path =0 solution and iteratively solve for other cases. c. Report the differences between iterative and non-iterative solution in terms of path delays. ID C = 1 Cz C4 Coff-path H 64

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get StartedRecommended Textbook for

Digital Systems Design Using Verilog

Authors: Charles Roth, Lizy K. John, Byeong Kil Lee

1st edition

1285051076, 978-1285051079

Students also viewed these Programming questions

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

View Answer in SolutionInn App