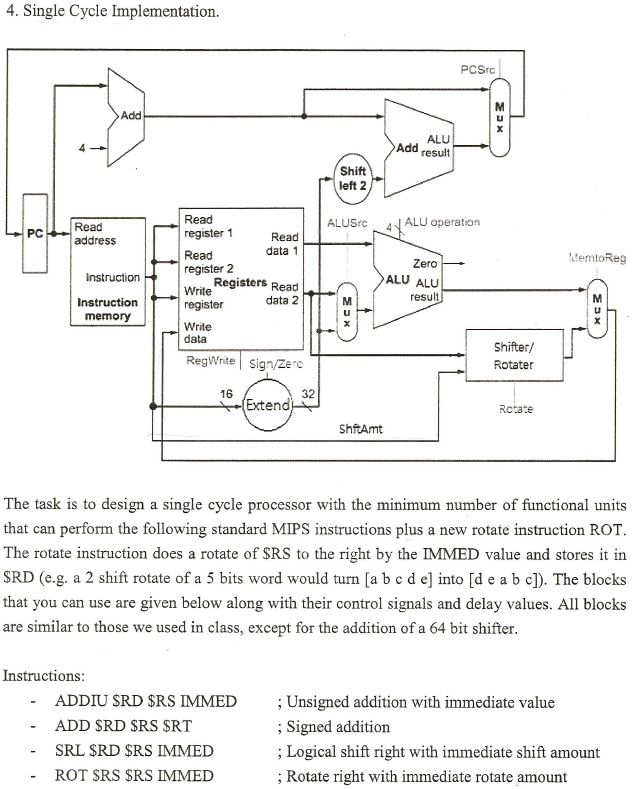

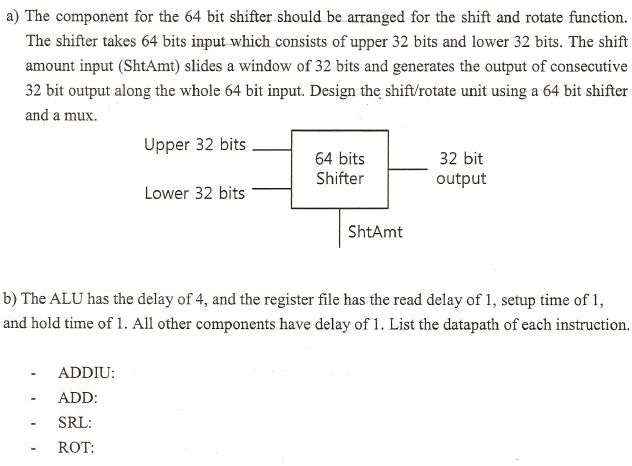

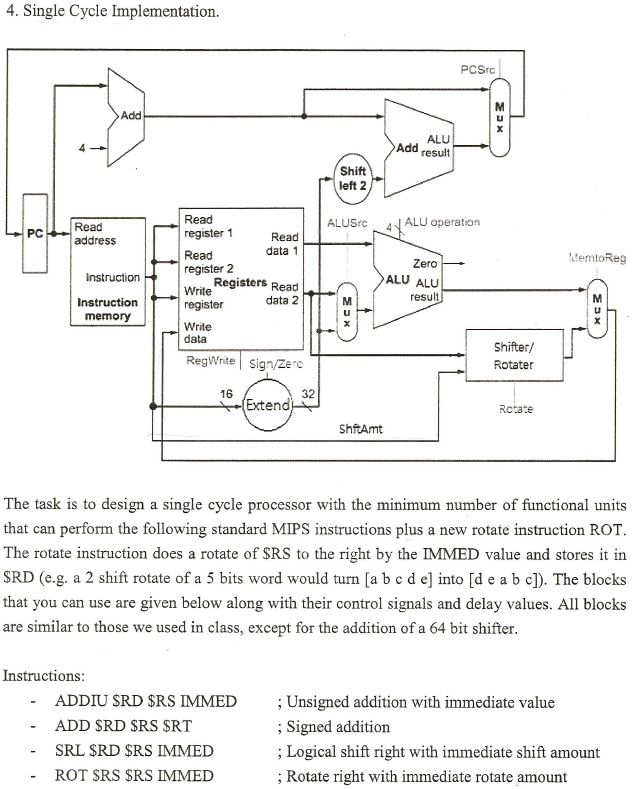

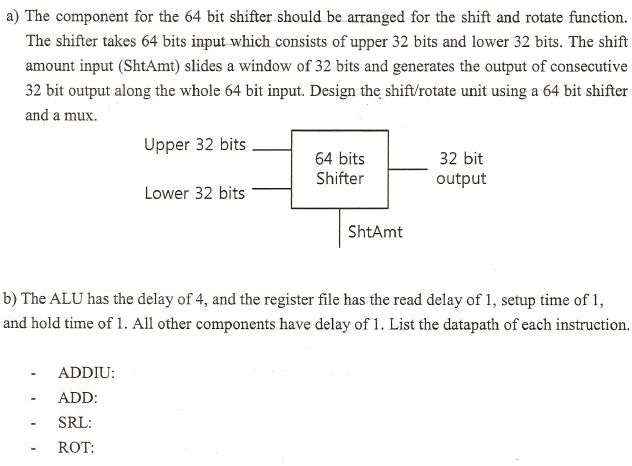

4. Single Cycle Implementation. PCSrc Add ALU Add result Shift left 2 Read ALU operation ALUSrc 4 Pec Read register 1 Read address data 1 Read emtoReg Zero register 2 instruction ALU ALU Registers Read Writer result Instruction data 2 register memory Write data shifter/ RegWrite Sign/zetc Rotater 16 32 Extend Rctate ShftAmt The task is to design a single cycle processor with the minimum number of functional units that can perform the following standard MIPS instructions plus a new rotate instruction ROT. The rotate instruction does a rotate of $RS to the right by the IMMED value and stores it in SRD (e.g. a 2 shift rotate of a 5 bits word would turn [a b c d el into Ld e a b cD. The blocks that you can use are given below along with their control signals and delay values. All blocks are similar to those we used in class, except for the addition of a 64 bit shifter. Instructions: ADDIUSRD SRS IMMED Unsigned addition with immediate value ADD SRD SRS $RT Signed addition SRL SRD SRS IMMED Logical shift right with immediate shift amount ROT SRS SRS IMMED Rotate right with immediate rotate amount 4. Single Cycle Implementation. PCSrc Add ALU Add result Shift left 2 Read ALU operation ALUSrc 4 Pec Read register 1 Read address data 1 Read emtoReg Zero register 2 instruction ALU ALU Registers Read Writer result Instruction data 2 register memory Write data shifter/ RegWrite Sign/zetc Rotater 16 32 Extend Rctate ShftAmt The task is to design a single cycle processor with the minimum number of functional units that can perform the following standard MIPS instructions plus a new rotate instruction ROT. The rotate instruction does a rotate of $RS to the right by the IMMED value and stores it in SRD (e.g. a 2 shift rotate of a 5 bits word would turn [a b c d el into Ld e a b cD. The blocks that you can use are given below along with their control signals and delay values. All blocks are similar to those we used in class, except for the addition of a 64 bit shifter. Instructions: ADDIUSRD SRS IMMED Unsigned addition with immediate value ADD SRD SRS $RT Signed addition SRL SRD SRS IMMED Logical shift right with immediate shift amount ROT SRS SRS IMMED Rotate right with immediate rotate amount