4-Bit Mini-CPU

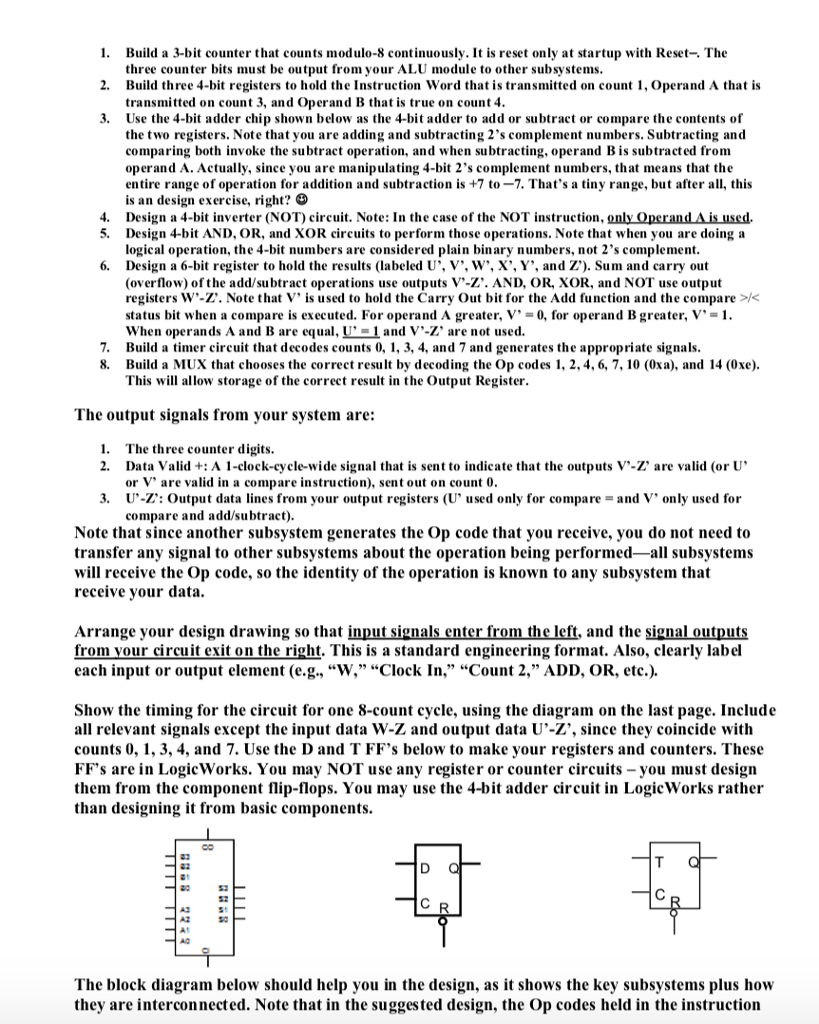

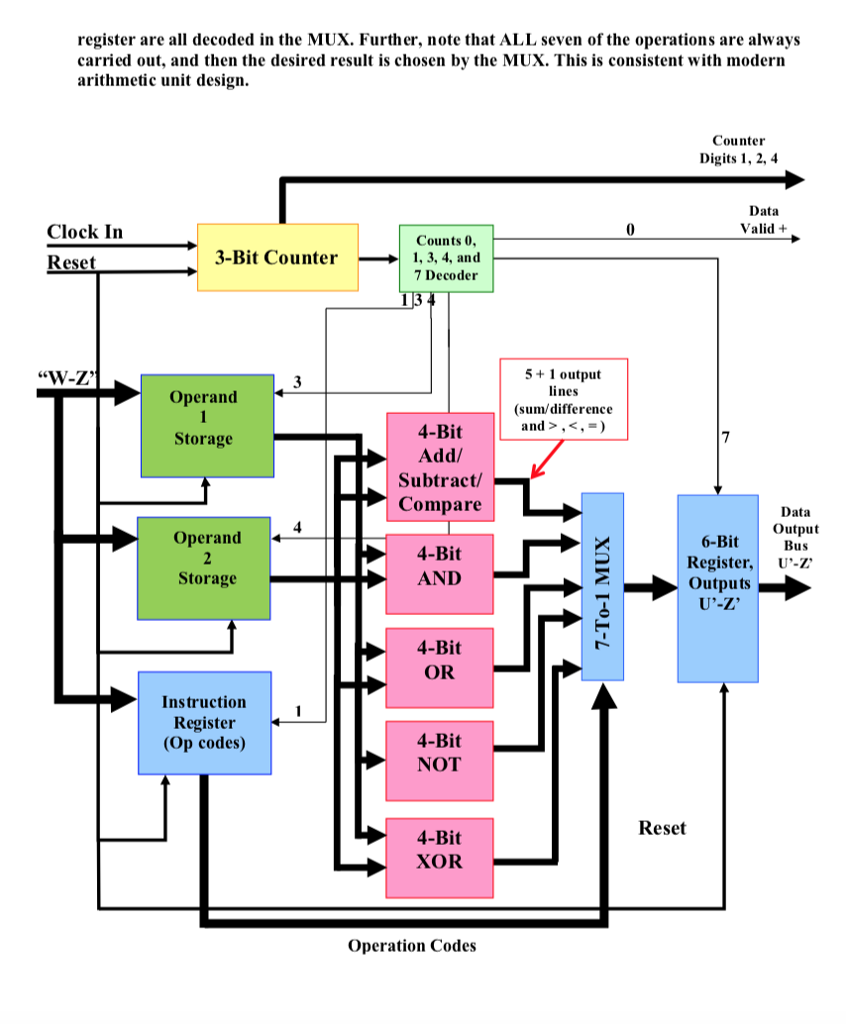

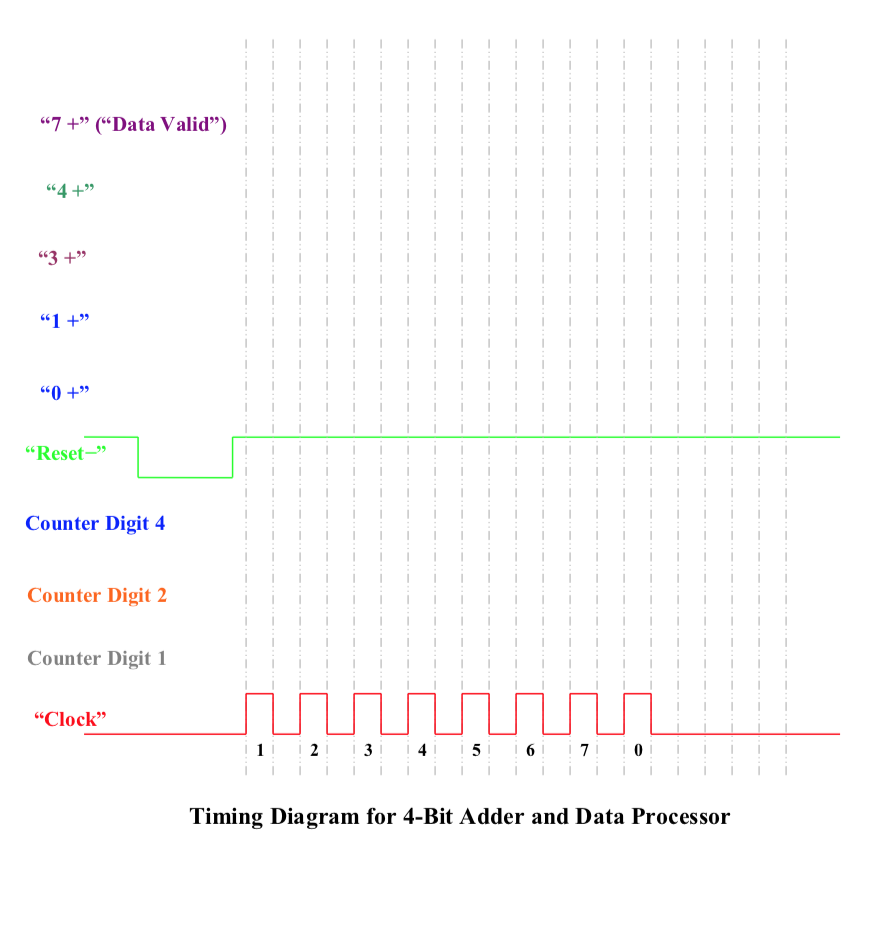

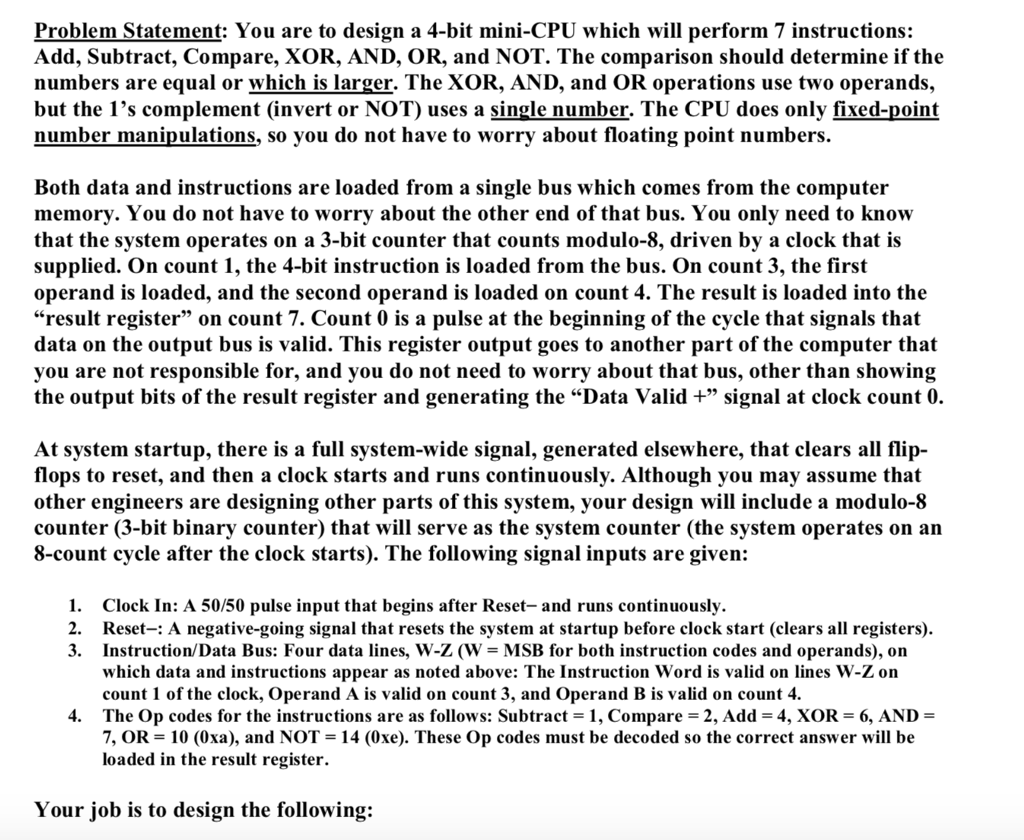

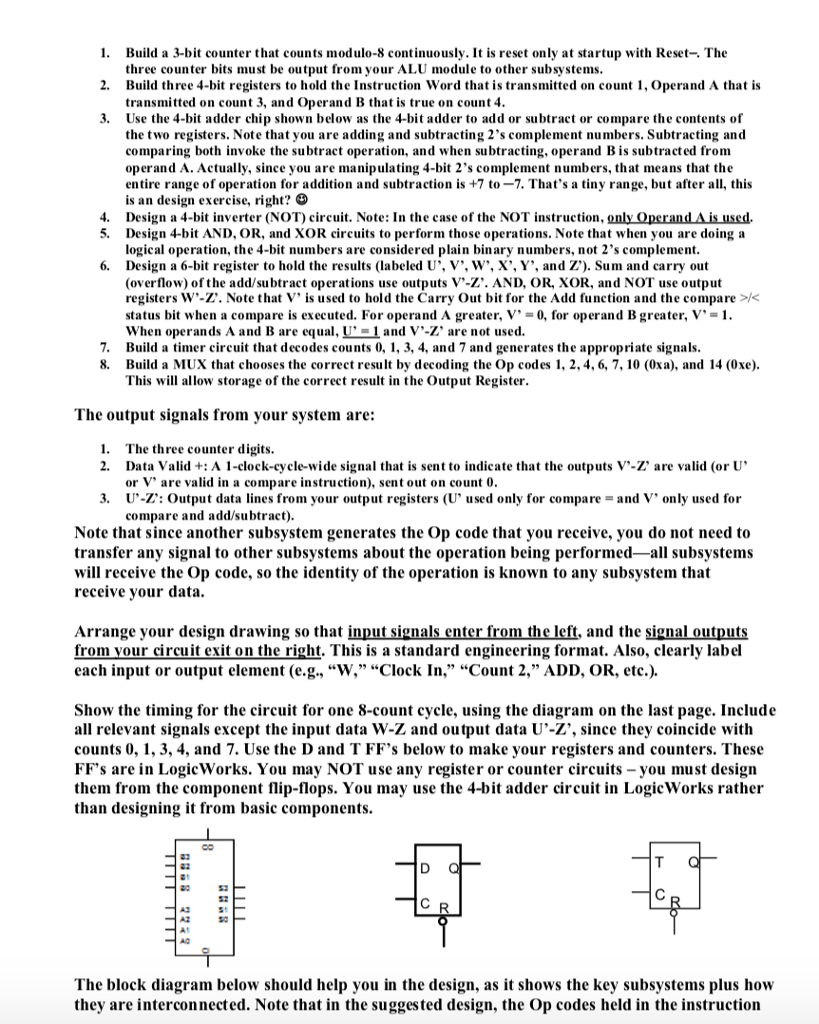

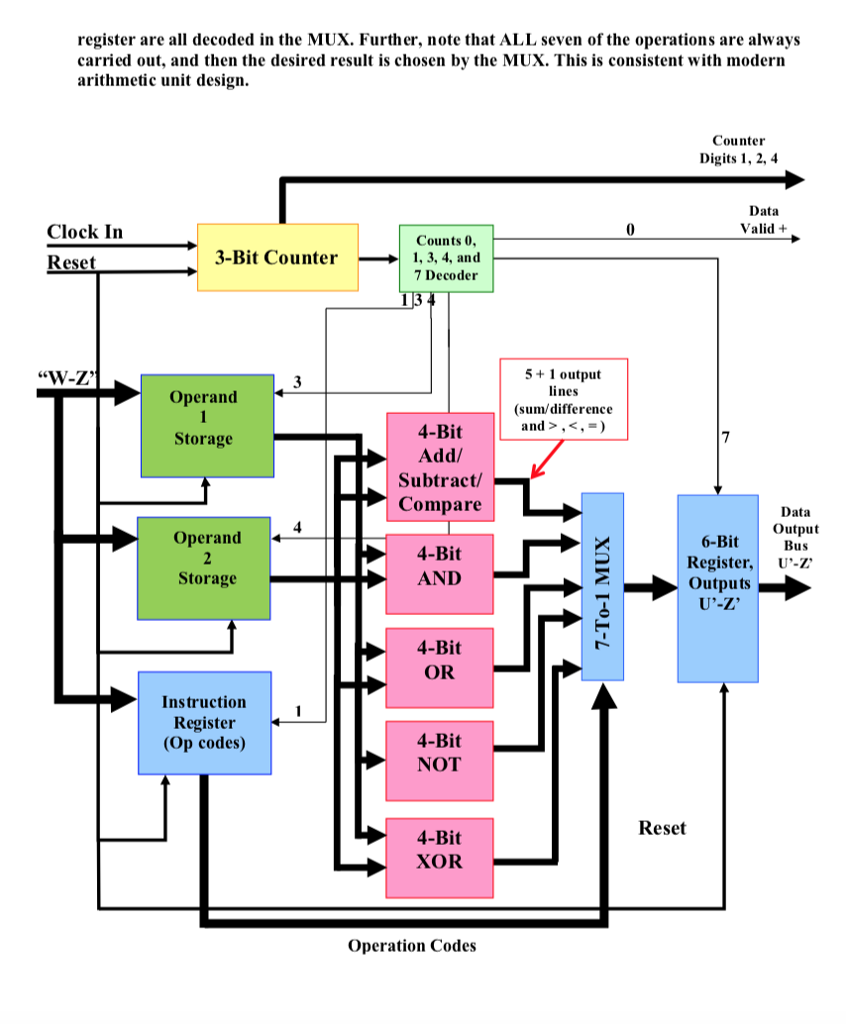

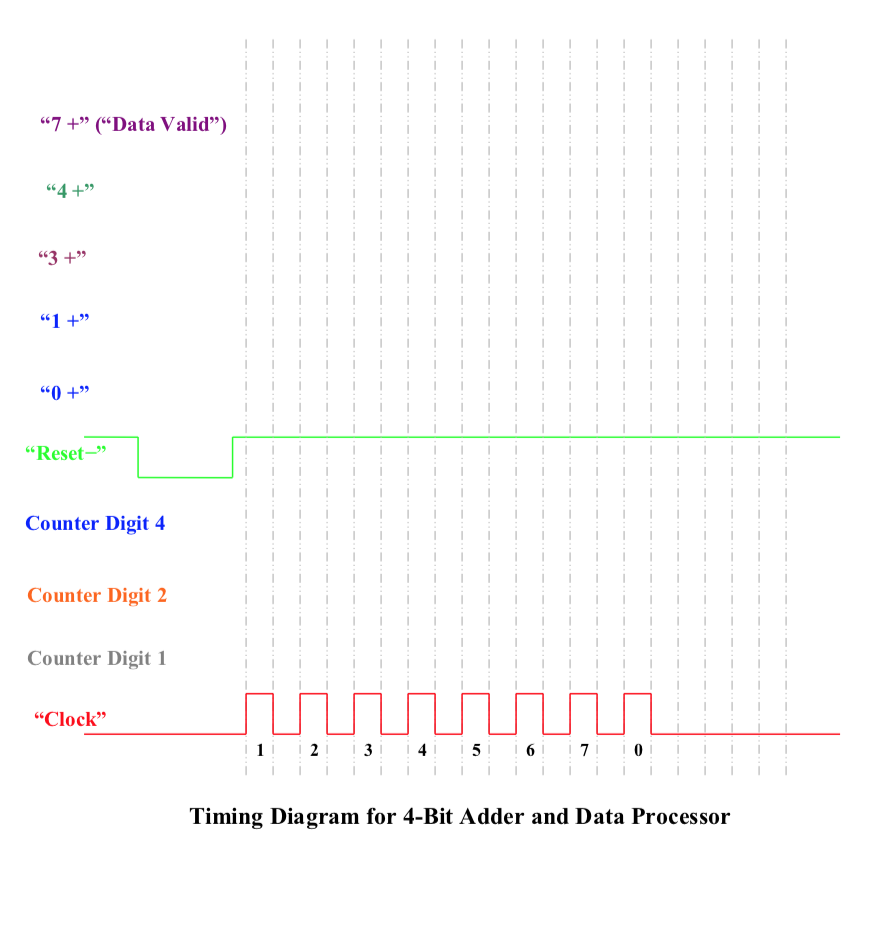

Problem Statement: You are to design a 4-bit mini-CPU which will perform 7 instructions: Add, Subtract, Compare, XOR, AND, OR, and NOT. The comparison should determine if the numbers are equal or which is larger. The XOR, AND, and OR operations use two operands, but the 1's complement (invert or NOT) uses a single number. The CPU does only fixed-point number manipulations, so you do not have to worry about floating point numbers. Both data and instructions are loaded from a single bus which comes from the computer memory. You do not have to worry about the other end of that bus. You only need to know that the system operates on a 3-bit counter that counts modulo-8, driven by a clock that is supplied. On count 1, the 4-bit instruction is loaded from the bus. On count 3, the first operand is loaded, and the second operand is loaded on count 4. The result is loaded into the result register" on count 7. Count 0 is a pulse at the beginning of the cycle that signals that data on the output bus is valid. This register output goes to another part of the computer that you are not responsible for, and you do not need to worry about that bus, other than showing the output bits of the result register and generating the "Data Valid +" signal at clock count 0 At system startup, there is a full system-wide signal, generated elsewhere, that clears all flip- flops to reset, and then a clock starts and runs continuously. Although you may assume that other engineers are designing other parts of this system, your design will include a modulo-8 counter (3-bit binary counter) that will serve as the system counter (the system operates on an 8-count cycle after the clock starts). The following signal inputs are given: 1. 2. 3. Clock In: A 50/50 pulse input that begins after Reset-and runs continuously. Reset-: A negative-going signal that resets the system at startup before clock start (clears all registers). Instruction/ Data Bus: Four data lines, w-Z (W = MSB for both instruction codes and operands), on which data and instructions appear as noted above: The Instruction Word is valid on lines W-Z on ount 1 of the clock, Operand A is valid on count 3, and Operand B is valid on count 4 The Op codes for the instructions are as follows: Subtract = 1, Compare = 2, Add 7, OR = 10 (0xa), and NOT = 14 (0xe). These Op codes must be decoded so the correct answer will be loaded in the result register. 4. 4, XOR-6, AND Your job is to design the following: Problem Statement: You are to design a 4-bit mini-CPU which will perform 7 instructions: Add, Subtract, Compare, XOR, AND, OR, and NOT. The comparison should determine if the numbers are equal or which is larger. The XOR, AND, and OR operations use two operands, but the 1's complement (invert or NOT) uses a single number. The CPU does only fixed-point number manipulations, so you do not have to worry about floating point numbers. Both data and instructions are loaded from a single bus which comes from the computer memory. You do not have to worry about the other end of that bus. You only need to know that the system operates on a 3-bit counter that counts modulo-8, driven by a clock that is supplied. On count 1, the 4-bit instruction is loaded from the bus. On count 3, the first operand is loaded, and the second operand is loaded on count 4. The result is loaded into the result register" on count 7. Count 0 is a pulse at the beginning of the cycle that signals that data on the output bus is valid. This register output goes to another part of the computer that you are not responsible for, and you do not need to worry about that bus, other than showing the output bits of the result register and generating the "Data Valid +" signal at clock count 0 At system startup, there is a full system-wide signal, generated elsewhere, that clears all flip- flops to reset, and then a clock starts and runs continuously. Although you may assume that other engineers are designing other parts of this system, your design will include a modulo-8 counter (3-bit binary counter) that will serve as the system counter (the system operates on an 8-count cycle after the clock starts). The following signal inputs are given: 1. 2. 3. Clock In: A 50/50 pulse input that begins after Reset-and runs continuously. Reset-: A negative-going signal that resets the system at startup before clock start (clears all registers). Instruction/ Data Bus: Four data lines, w-Z (W = MSB for both instruction codes and operands), on which data and instructions appear as noted above: The Instruction Word is valid on lines W-Z on ount 1 of the clock, Operand A is valid on count 3, and Operand B is valid on count 4 The Op codes for the instructions are as follows: Subtract = 1, Compare = 2, Add 7, OR = 10 (0xa), and NOT = 14 (0xe). These Op codes must be decoded so the correct answer will be loaded in the result register. 4. 4, XOR-6, AND Your job is to design the following