Question

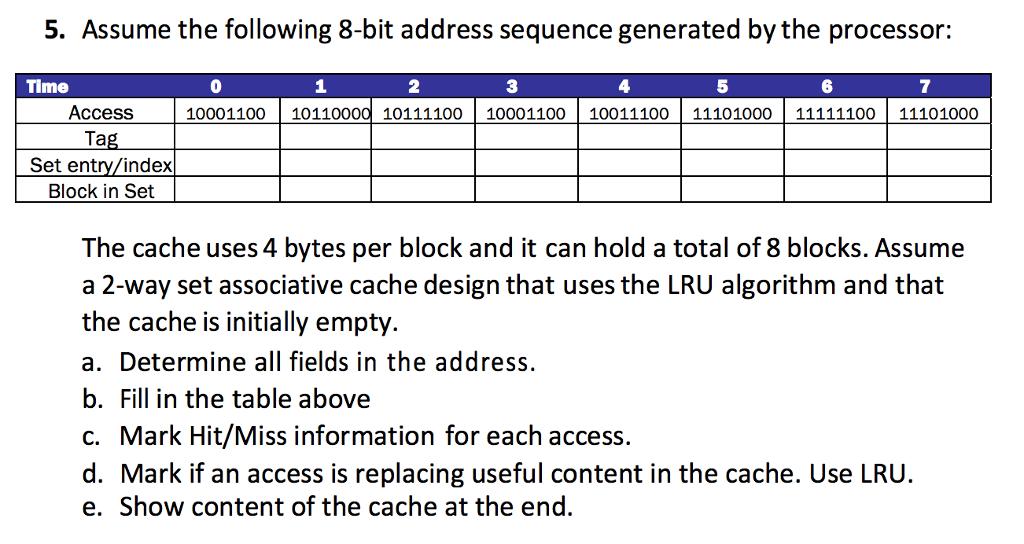

5. Assume the following 8-bit address sequence generated by the processor: 2 10110000 10111100 Time 1 Access Tag 10001100 Set entry/index Block in Set

5. Assume the following 8-bit address sequence generated by the processor: 2 10110000 10111100 Time 1 Access Tag 10001100 Set entry/index Block in Set 3 5 6 7 10001100 10011100 11101000 11111100 11101000 The cache uses 4 bytes per block and it can hold a total of 8 blocks. Assume a 2-way set associative cache design that uses the LRU algorithm and that the cache is initially empty. a. Determine all fields in the address. b. Fill in the table above c. Mark Hit/Miss information for each access. d. Mark if an access is replacing useful content in the cache. Use LRU. e. Show content of the cache at the end.

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get StartedRecommended Textbook for

Income Tax Fundamentals 2013

Authors: Gerald E. Whittenburg, Martha Altus Buller, Steven L Gill

31st Edition

1111972516, 978-1285586618, 1285586611, 978-1285613109, 978-1111972516

Students also viewed these Programming questions

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

View Answer in SolutionInn App