Question

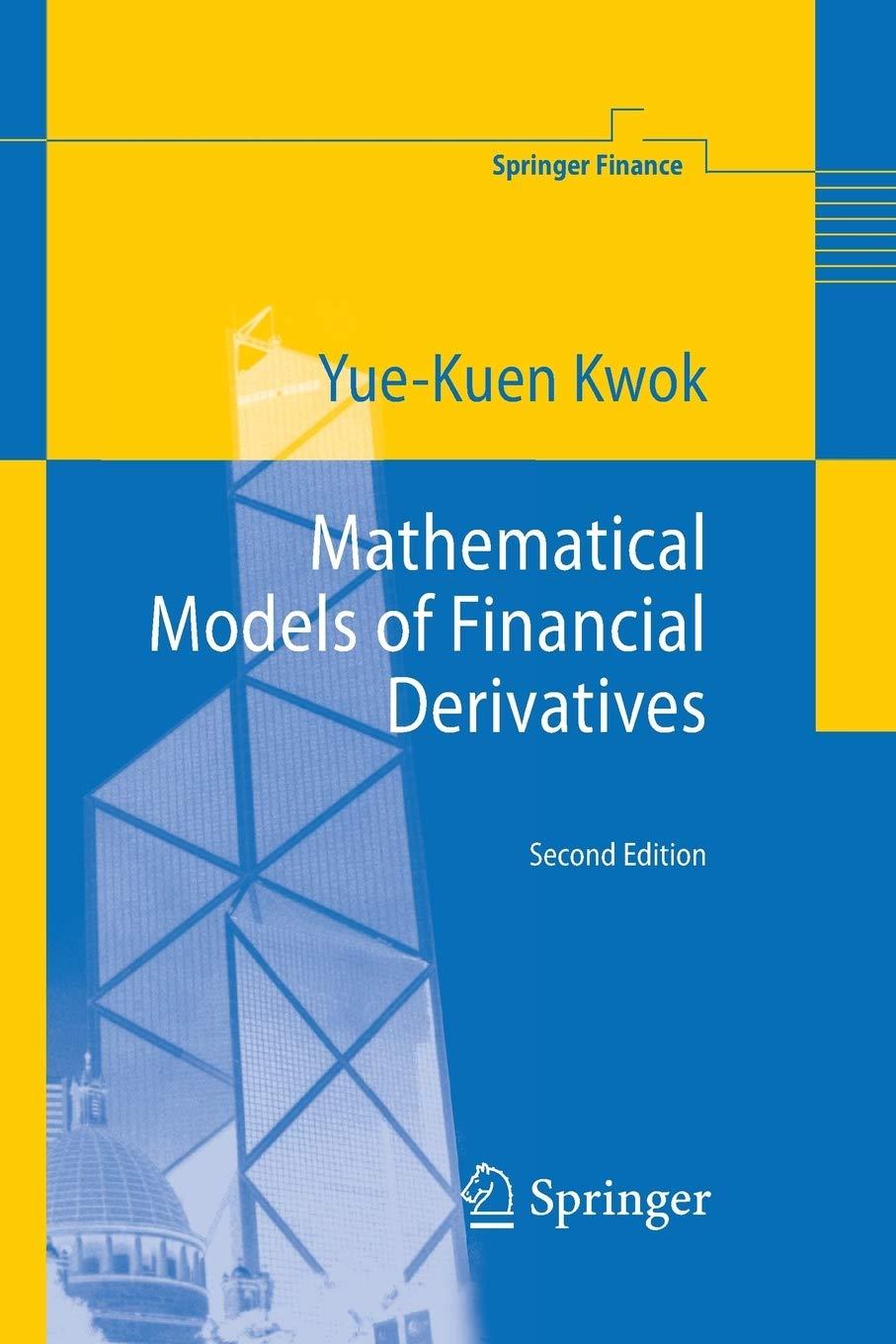

6. Design a synchronous sequential circuit that has an input w and an output z. The circuit acts as a sequence edge detector: z=1

6. Design a synchronous sequential circuit that has an input w and an output z. The circuit acts as a sequence edge detector: z=1 when the input bit stream changes from 0 to 1 or from 1 to 0, otherwise z=0. a. Define the states and give the state diagram or FSM (either Moore machine or Mealy machine) [10 pts] b. Give the state transition table with the inputs to the JK flip flops and the output. [5pts] c. Draw the schematic of the circuit using the above specified components and logic gates. [5 pts]

Step by Step Solution

There are 3 Steps involved in it

Step: 1

a State Definition and State Diagram In this sequence edge detector circuit we can define two states ...

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get StartedRecommended Textbook for

Mathematical Models Of Financial Derivative

Authors: Yue-Kuen Kwok

2nd Edition

3642447937, 978-3642447938

Students also viewed these Programming questions

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

View Answer in SolutionInn App