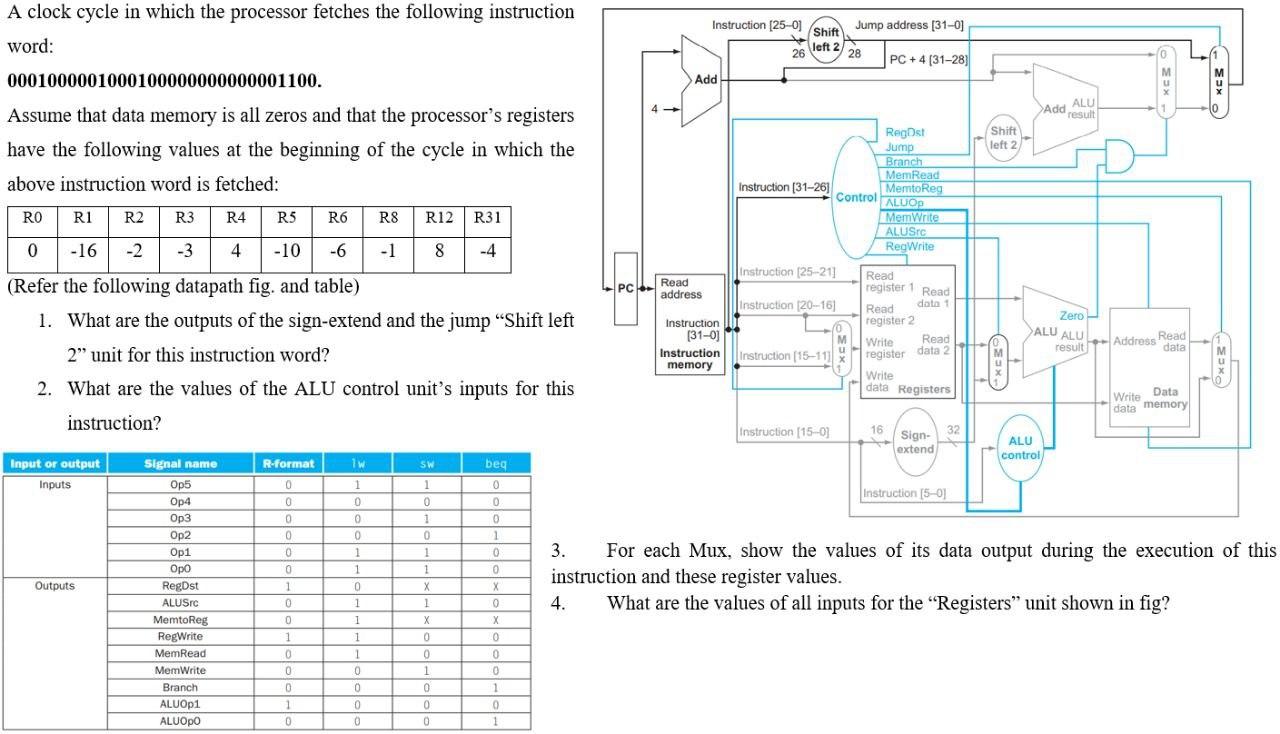

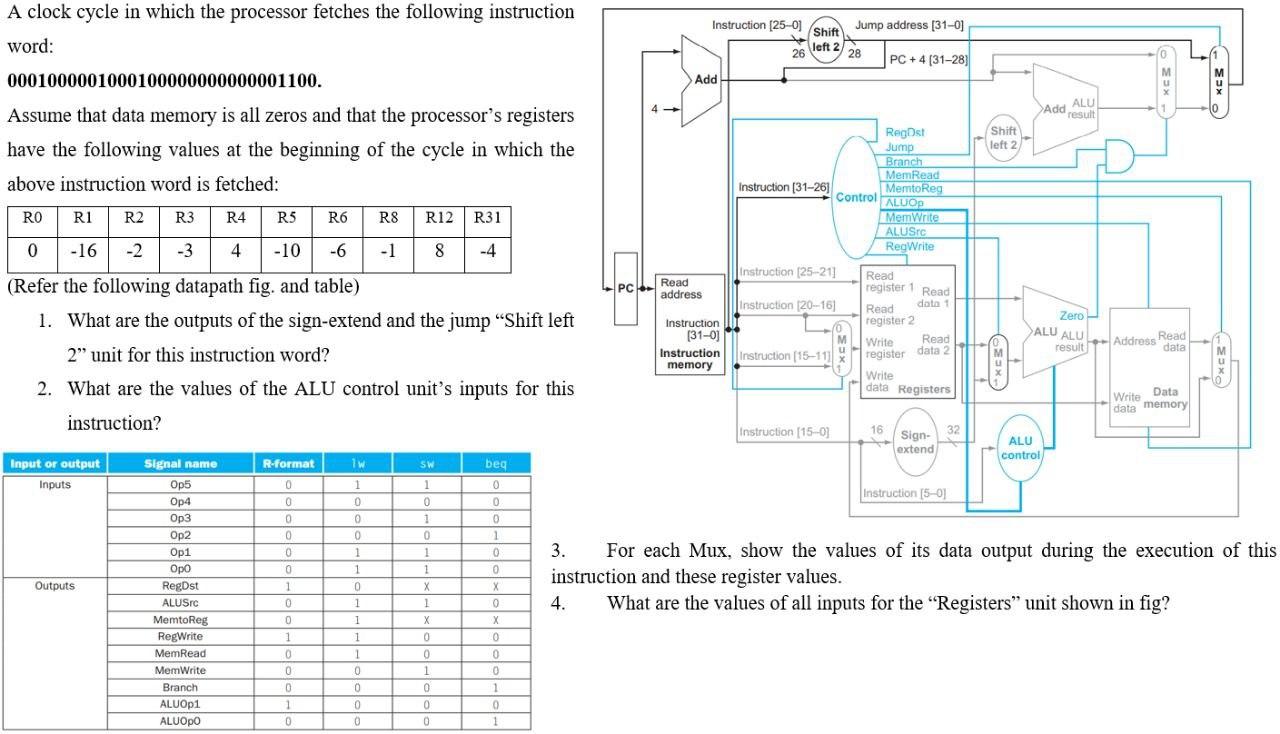

A clock cycle in which the processor fetches the following instruction word: Instruction (25-01 Jump address (31-0) Shift left 2 26 28 PC +4 (31-28) Add M u M 4- Add ALU > 0 result 0001000001000100000000000001100. Assume that data memory is all zeros and that the processor's registers have the following values at the beginning of the cycle in which the above instruction word is fetched: Shift left 2 RegDst Jump Branch MemRead Merto Reg Instruction (31-26) ( Control ALUOD RO R1 R2 R3 R4 R5 R6 R8 R12 R31 MemWrite ALUSrc RegWrite 0 -16 -2 -3 4 -10 -6 -1 8 -4 PCH. Read Instruction (25-211 address instruction (20--16] Instruction 10 (31-01 M Instruction Instruction (15-11 memory Read register 1 Read Read data 1 register 2 Write Read Zero SALU ALU (Refer the following datapath fig. and table) 1. What are the outputs of the sign-extend and the jump Shift left 2" unit for this instruction word? 2. What are the values of the ALU control unit's inputs for this instruction? M data register data 2 result Address Read iluxe| Write data Registers Write Data data memory Instruction (15-01 16 32 Sign- extend ALU control 1W SW Input or output Inputs Signal name Op5 Op4 Op3 beg 0 0 Instruction 15-01 R-format 0 0 0 0 0 0 1 0 0 0 1 1 1 0 1 0 1 1 0 0 1 1 O Outputs 3. 3 For each Mux, show the values of its data output during the execution of this instruction and these register values. 4. . What are the values of all inputs for the Registers unit shown in fig? X 0 Op2 Opi RegDst ALUSC MemtoReg RegWrite MemRead MemWrite Branch ALUOp1 ALUOPO 0 1 0 0 0 1 0 0 0 1 0 0 1 1 1 1 0 0 X 1 X X 0 0 1 0 0 0 X 0 0 0 1 0 1 0 0 A clock cycle in which the processor fetches the following instruction word: Instruction (25-01 Jump address (31-0) Shift left 2 26 28 PC +4 (31-28) Add M u M 4- Add ALU > 0 result 0001000001000100000000000001100. Assume that data memory is all zeros and that the processor's registers have the following values at the beginning of the cycle in which the above instruction word is fetched: Shift left 2 RegDst Jump Branch MemRead Merto Reg Instruction (31-26) ( Control ALUOD RO R1 R2 R3 R4 R5 R6 R8 R12 R31 MemWrite ALUSrc RegWrite 0 -16 -2 -3 4 -10 -6 -1 8 -4 PCH. Read Instruction (25-211 address instruction (20--16] Instruction 10 (31-01 M Instruction Instruction (15-11 memory Read register 1 Read Read data 1 register 2 Write Read Zero SALU ALU (Refer the following datapath fig. and table) 1. What are the outputs of the sign-extend and the jump Shift left 2" unit for this instruction word? 2. What are the values of the ALU control unit's inputs for this instruction? M data register data 2 result Address Read iluxe| Write data Registers Write Data data memory Instruction (15-01 16 32 Sign- extend ALU control 1W SW Input or output Inputs Signal name Op5 Op4 Op3 beg 0 0 Instruction 15-01 R-format 0 0 0 0 0 0 1 0 0 0 1 1 1 0 1 0 1 1 0 0 1 1 O Outputs 3. 3 For each Mux, show the values of its data output during the execution of this instruction and these register values. 4. . What are the values of all inputs for the Registers unit shown in fig? X 0 Op2 Opi RegDst ALUSC MemtoReg RegWrite MemRead MemWrite Branch ALUOp1 ALUOPO 0 1 0 0 0 1 0 0 0 1 0 0 1 1 1 1 0 0 X 1 X X 0 0 1 0 0 0 X 0 0 0 1 0 1 0 0