Question: a. Hardware Virtual Memory Page Miss Handling: The requested address is not in the Translation Lookaside Buffer (TLB). The CPU automatically checks the page tables

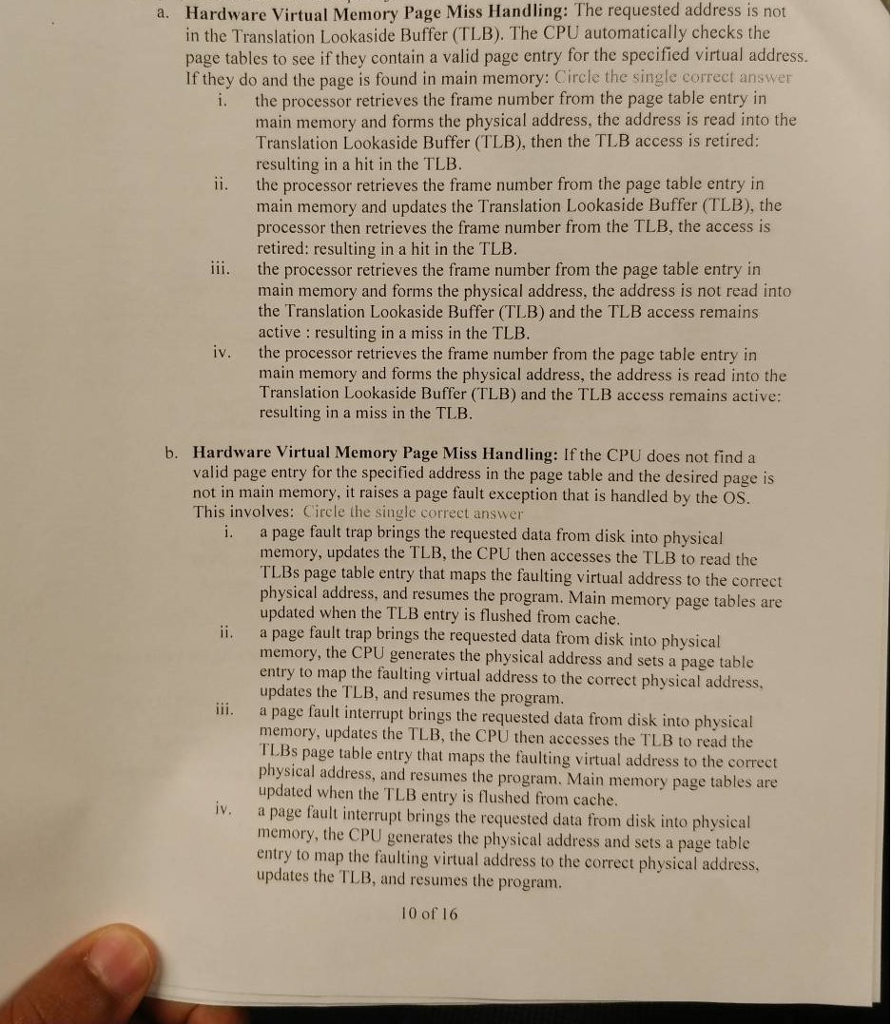

a. Hardware Virtual Memory Page Miss Handling: The requested address is not in the Translation Lookaside Buffer (TLB). The CPU automatically checks the page tables to see if they contain a valid page entry for the specified virtual address If they do and the page is found in main memory: Circle the single correct answer the processor retrieves the frame number from the page table entry in main memory and forms the physical address, the address is read into the Translation Lookaside Buffer (TLB), then the TLB access is retired resulting in a hit in the TLB i. the processor retrieves the frame number from the page table entry in main memory and updates the Translation Lookaside Buffer (TLB), the processor then retrieves the frame number from the TLB, the access retired: resulting in a hit in the TLB ii. the processor retrieves the frame number from the page table entry in main memory and forms the physical address, the address is not read into the Translation Lookaside Buffer (TLB) and the TLB access remains active : resulting in a miss in the TLB the processor retrieves the frame number from the page table entry in main memory and forms the physical address, the address is read into the Translation Lookaside Buffer (TLB) and the TLB access remains active: resulting in a miss in the TLB Hardware Virtual Memory Page Miss Handling: If the CPU does not find a valid page entry for the specified address in the page table and the desired page is not in main memory, it raises a page fault exception that is handled by the OS This involves: Cirele the single correct answer b. a page fault trap brings the requested data from disk into physical memory, updates the TLB, the CPU then accesses the TLB to read the TLBs page table entry that maps the faulting virtual address to the correct physical address, and resumes the program. Main memory page tables are updated when the TLB entry is flushed from cache i. page fault trap brings the requested data from disk into physical memory, the CPU generates the physical address and sets a page table entry to map the faulting virtual address to the correct physical address updates the TLB, and resumes the program page fault interrupt brings the requested data from disk into physical memory, updates the TLB, the CPU then accesses the TLB to read the TLBs page table entry that maps the faulting virtual address to the correct physical address, and resumes the program. Main memory page tab updated when the TLB entry is flushed from cache ii. a ii. a iv. a page fault interrupt brings the requested data from disk into physical memory, the CPU generates the physical address and sets a page table entry to map the faulting virtual address to the correct physical address updates the TLB, and resumes the program 10 of 16

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts