Answered step by step

Verified Expert Solution

Question

1 Approved Answer

(a) (i) Derive the equation that describes C4 in the 4-bit carry lookahead adder in terms of the propagate, generate and carry signals of

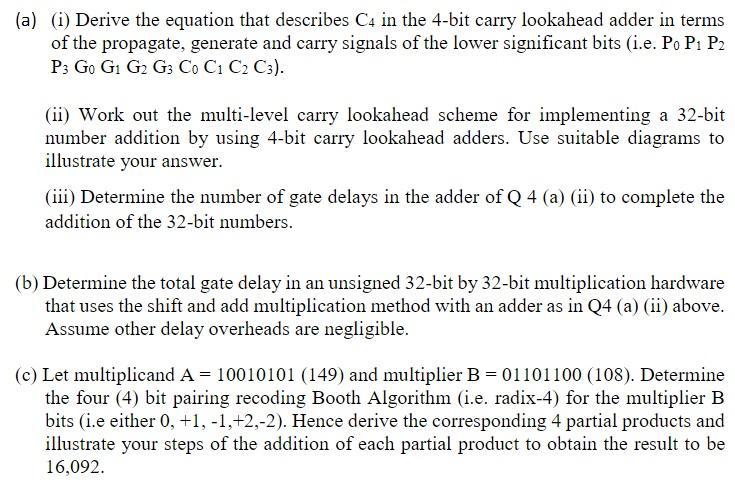

(a) (i) Derive the equation that describes C4 in the 4-bit carry lookahead adder in terms of the propagate, generate and carry signals of the lower significant bits (i.e. Po P1 P2 P3 Go G1 G2 G3 C0 C1 C2 C3). (ii) Work out the multi-level carry lookahead scheme for implementing a 32-bit number addition by using 4-bit carry lookahead adders. Use suitable diagrams to illustrate your answer. (iii) Determine the number of gate delays in the adder of Q 4 (a) (ii) to complete the addition of the 32-bit numbers. (b) Determine the total gate delay in an unsigned 32-bit by 32-bit multiplication hardware that uses the shift and add multiplication method with an adder as in Q4 (a) (ii) above. Assume other delay overheads are negligible. (c) Let multiplicand A = 10010101 (149) and multiplier B = 01101100 (108). Determine the four (4) bit pairing recoding Booth Algorithm (i.e. radix-4) for the multiplier B bits (i.e either 0, +1, -1,+2,-2). Hence derive the corresponding 4 partial products and illustrate your steps of the addition of each partial product to obtain the result to be 16,092.

Step by Step Solution

★★★★★

3.44 Rating (163 Votes )

There are 3 Steps involved in it

Step: 1

a i To derive the equation for C4 in a 4bit carry lookahead adder we can use the following logic C4 G3 P3 G2 P3 P2 G1 P3 P2 P1 G0 P3 P2 P1 P0 C0 Here ...

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started