Answered step by step

Verified Expert Solution

Question

1 Approved Answer

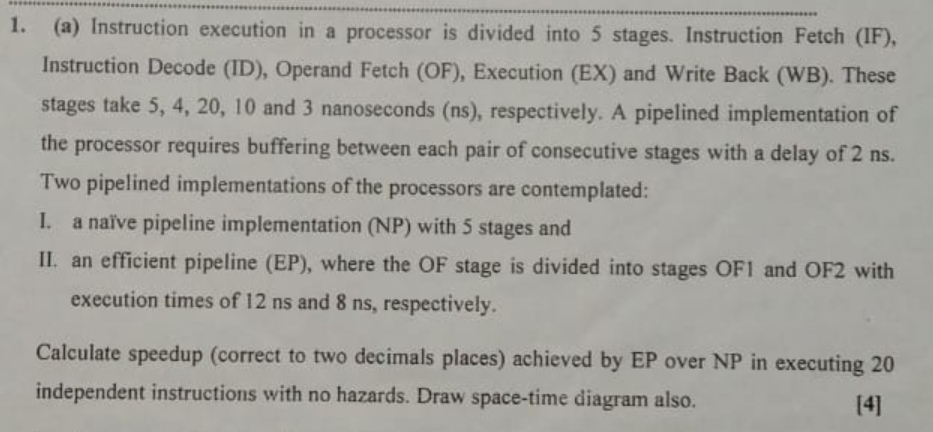

( a ) Instruction execution in a processor is divided into 5 stages. Instruction Fetch ( IF ) , Instruction Decode ( ID ) ,

a Instruction execution in a processor is divided into stages. Instruction Fetch IF Instruction Decode ID Operand Fetch OF Execution EX and Write Back WB These stages take and nanoseconds ns respectively. A pipelined implementation of the processor requires buffering between each pair of consecutive stages with a delay of Two pipelined implementations of the processors are contemplated: I. a nave pipeline implementation NP with stages and II an efficient pipeline EP where the OF stage is divided into stages OF and OF with execution times of and respectively. Calculate speedup correct to two decimals places achieved by EP over NP in executing independent instructions with no hazards. Draw spacetime diagram also.

a Instruction execution in a processor is divided into stages. Instruction Fetch IF Instruction Decode ID Operand Fetch OF Execution EX and Write Back WB These stages take and nanoseconds ns respectively. A pipelined implementation of the processor requires buffering between each pair of consecutive stages with a delay of Two pipelined implementations of the processors are contemplated:

I. a nave pipeline implementation NP with stages and

II an efficient pipeline EP where the OF stage is divided into stages OF and OF with execution times of and respectively.

Calculate speedup correct to two decimals places achieved by EP over NP in executing independent instructions with no hazards. Draw spacetime diagram also.

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started