Question

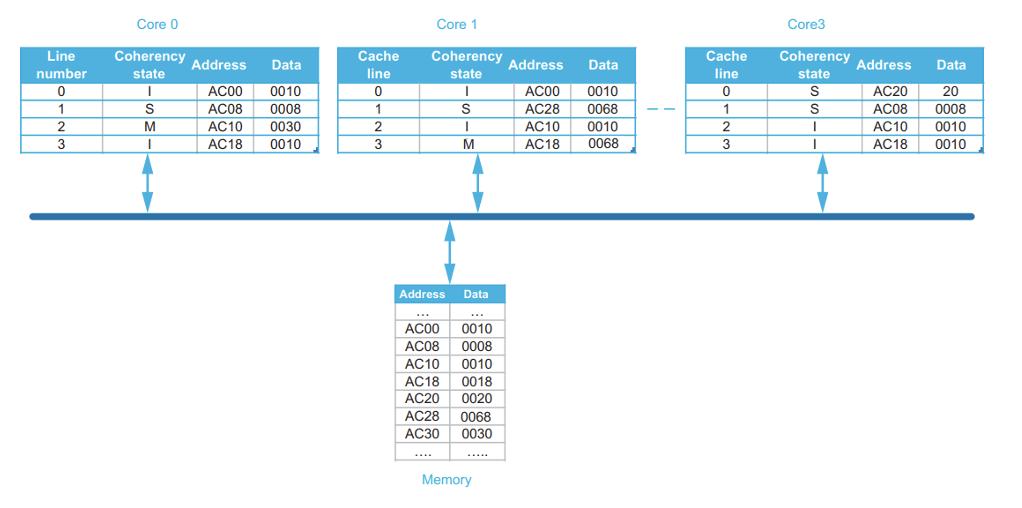

A multicore SMT multiprocessor is illustrated in the following picture. Only the cache contents are shown. Each core has a single, private cache with coherence

A multicore SMT multiprocessor is illustrated in the following picture. Only the cache contents are shown. Each core has a single, private cache with coherence maintained using the snooping coherence protocol. Each cache is direct-mapped, with four lines, each holding 2 bytes (to simplify diagram). For further simplification, the whole line addresses in memory are shown in the address fields in the caches, where the tag would normally exist. The coherence states are denoted M, S, and I for Modified, Shared, and Invalid.

Show the resulting state (i.e., coherence state, tags, and data) of the caches and memory after the actions given below (actions do not depend on one another). Show only the cache lines that are related.

A) C3 wants to read AC 18

B) C0 wants to write 0080 to AC28

C) C3 wants to write 0020 to AC10

D) C1 wants to read AC 00

C) C3 wants to read AC20

Line number 0 1 2 3 Core 0 Coherency state T S M 1 Data AC00 0010 AC08 0008 AC10 0030 AC18 0010 Address Cache line 0 1 2 3 Core 1 Coherency state I S I M Address Data AC00 0010 AC08 0008 AC10 0010 AC18 0018 AC20 0020 AC28 0068 AC30 0030 Memory Address Data AC00 0010 AC28 0068 AC10 0010 AC18 0068 Cache line 0 1 2 3 Core3 Coherency state S S I I Address AC20 AC08 AC10 AC18 Data 20 0008 0010 0010

Step by Step Solution

3.44 Rating (147 Votes )

There are 3 Steps involved in it

Step: 1

Solution Struct node next Top NULL Main Struct nodenew New Struct node mallocsize ofstr...

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started