Answered step by step

Verified Expert Solution

Question

1 Approved Answer

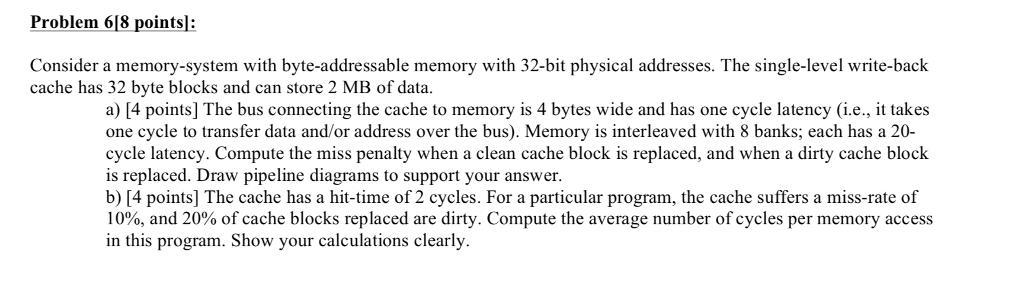

Problem 618 points]: Consider a memory-system with byte-addressable memory with 32-bit physical addresses. The single-level write-back cache has 32 byte blocks and can store

Problem 618 points]: Consider a memory-system with byte-addressable memory with 32-bit physical addresses. The single-level write-back cache has 32 byte blocks and can store 2 MB of data. a) [4 points] The bus connecting the cache to memory is 4 bytes wide and has one cycle latency (i.e., it takes one cycle to transfer data and/or address over the bus). Memory is interleaved with 8 banks; each has a 20- cycle latency. Compute the miss penalty when a clean cache block is replaced, and when a dirty cache block is replaced. Draw pipeline diagrams to support your answer. b) [4 points] The cache has a hit-time of 2 cycles. For a particular program, the cache suffers a miss-rate of 10%, and 20% of cache blocks replaced are dirty. Compute the average number of cycles per memory access in this program. Show your calculations clearly.

Step by Step Solution

★★★★★

3.53 Rating (156 Votes )

There are 3 Steps involved in it

Step: 1

a Solution For a clean cache block the miss penalty is 29 cycl...

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started