Question

A TLB contains three entries and uses LRU for the replacement policy. Initially, TLB entries are empty. Following is the trace. Note that A,B,C

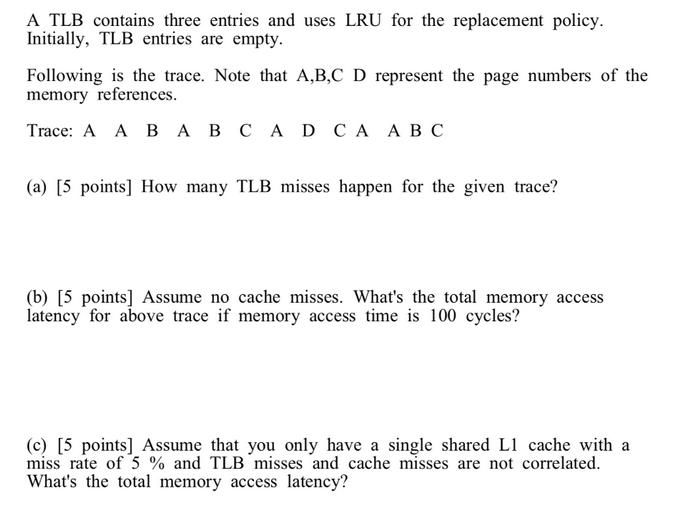

A TLB contains three entries and uses LRU for the replacement policy. Initially, TLB entries are empty. Following is the trace. Note that A,B,C D represent the page numbers of the memory references. Trace: A A B A B C AD CA ABC (a) [5 points] How many TLB misses happen for the given trace? (b) [5 points] Assume no cache misses. What's the total memory access latency for above trace if memory access time is 100 cycles? (c) [5 points] Assume that you only have a single shared L1 cache with a miss rate of 5% and TLB misses and cache misses are not correlated. What's the total memory access latency?

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get StartedRecommended Textbook for

Computer organization and architecture designing for performance

Authors: william stallings

8th edition

136073735, 978-0136073734

Students also viewed these Programming questions

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

View Answer in SolutionInn App