Any Verilog help is much appreciated, having trouble with these problems, so far i have the written a code that calls a module 4 times for each bit. The test errors are not of concern in this assignment, I wrote the code so it will produce an error when (a>b) & (a==b) or any of the test conditions are equal.

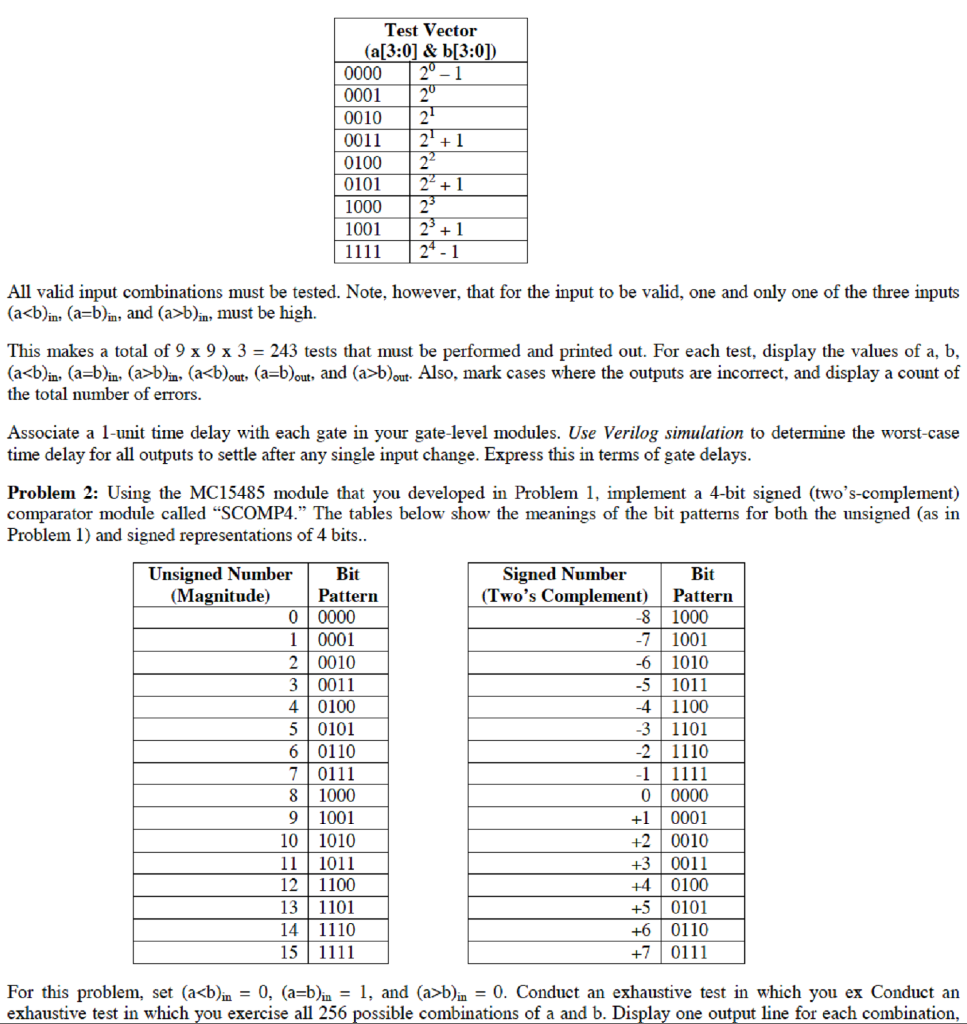

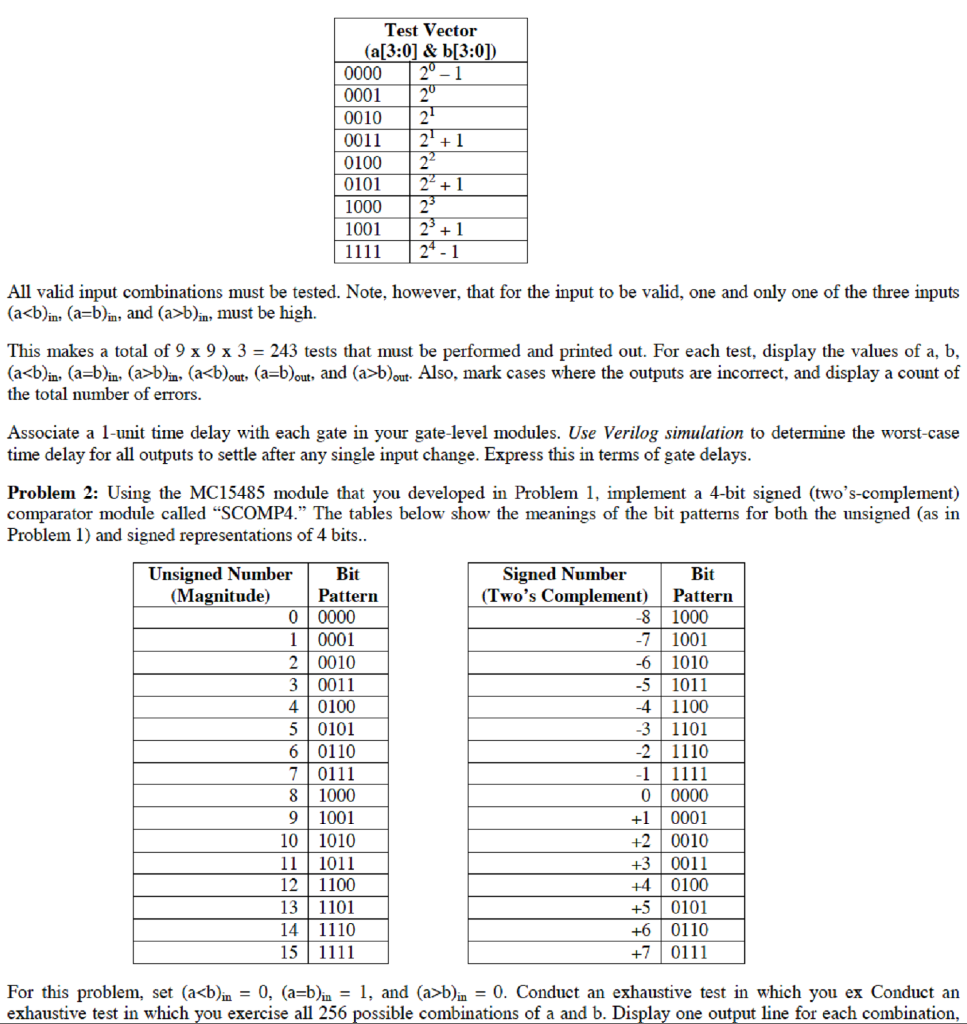

1.Using Verilog gate-level and structural specification, construct a simulation of the MC14585 4-bit Magnitude Comparator, whose schematic is shown on the data sheet. Define enough modules so that you have to describe redundant sub-circuits only once. Include a top-level stimulus module (test bench) that will exercise your design. Apply all the combinations of the following test vectors in the indicated order to the a and b inputs of the comparator (there are 8x8=64 combinations).

Test Vector (a[3:0] & b[3:0]) 00002-1 0001- 0010 2 0011 2 + 1 01002 01012 1 10002 1001231 All valid input combinations must be tested. Note, however, that for the input to be valid, one and only one of the three inputs (a-b)a, (a-b)in, and (a>b)a, must be high. This makes a total of 9 x 9 x 3 = 243 tests that must be performed and printed out. For each test, display the values of a, b, (a-b) (a-b) , (a>b) , (a

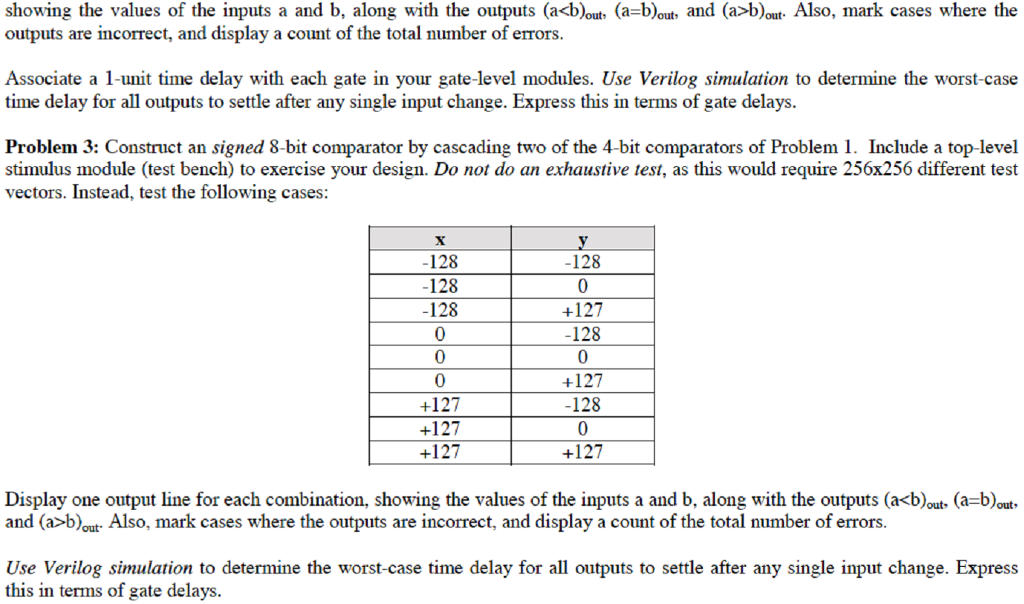

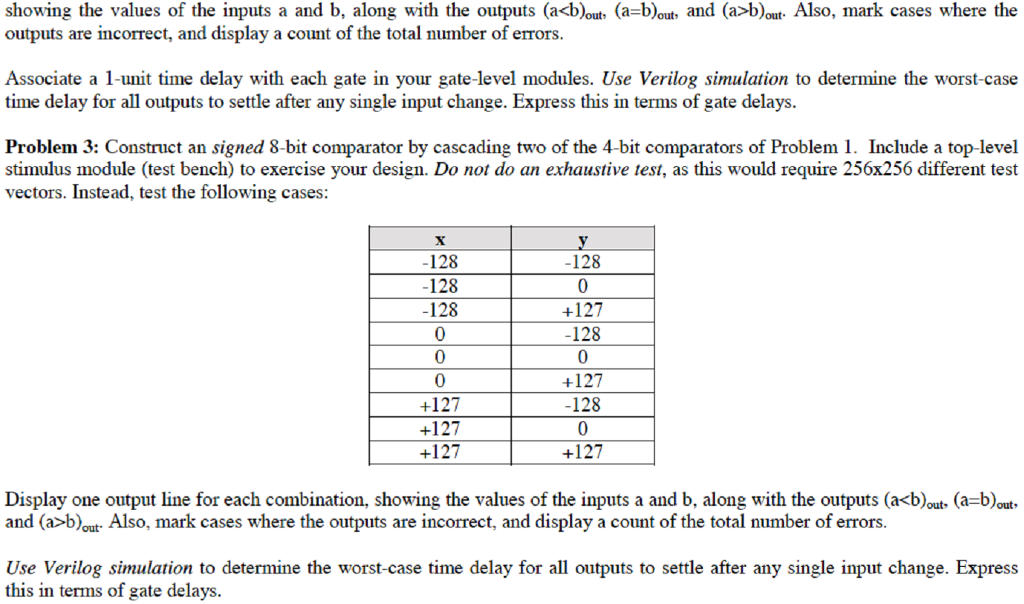

b)out Also, mark cases where the outputs are incorrect, and display a count of the total number of errors. Associate a l-unit time delay with each gate in your gate-level modules. Use Verilog simulation to determine the worst-case time delay for all outputs to settle after any single input change. Express this in terms of gate delays Problem 2: Using the MC15485 module that you developed in Problem 1, implement a 4-bit signed (two's-complement) comparator module called "SCOMP4." The tables below show the meanings of the bit patterns for both the unsigned (as in Problem 1) and signed representations of 4 bits Unsigned Number (Magnitude) Signed Number (Two's Complement Pattern Bit Bit Patterin 8 1000 7 1001 6 1010 5 1011 4 1100 3 1101 2 1110 0001 20010 3 0011 4 0100 5 0101 6 0110 7 0111 8 1000 91001 10 1010 111011 12 1100 13 1101 14 1110 +1 0001 +2 0010 +3 0011 +4 0100 +5 0101 +6 0110 +7 0111 For this problem, set (ab)a-0. Conduct an exhaustive test in which you ex Conduct an exhaustive test in which you exercise all 256 possible combinations of a and b. Display one output line for each combination Test Vector (a[3:0] & b[3:0]) 00002-1 0001- 0010 2 0011 2 + 1 01002 01012 1 10002 1001231 All valid input combinations must be tested. Note, however, that for the input to be valid, one and only one of the three inputs (a-b)a, (a-b)in, and (a>b)a, must be high. This makes a total of 9 x 9 x 3 = 243 tests that must be performed and printed out. For each test, display the values of a, b, (a-b) (a-b) , (a>b) , (ab)out Also, mark cases where the outputs are incorrect, and display a count of the total number of errors. Associate a l-unit time delay with each gate in your gate-level modules. Use Verilog simulation to determine the worst-case time delay for all outputs to settle after any single input change. Express this in terms of gate delays Problem 2: Using the MC15485 module that you developed in Problem 1, implement a 4-bit signed (two's-complement) comparator module called "SCOMP4." The tables below show the meanings of the bit patterns for both the unsigned (as in Problem 1) and signed representations of 4 bits Unsigned Number (Magnitude) Signed Number (Two's Complement Pattern Bit Bit Patterin 8 1000 7 1001 6 1010 5 1011 4 1100 3 1101 2 1110 0001 20010 3 0011 4 0100 5 0101 6 0110 7 0111 8 1000 91001 10 1010 111011 12 1100 13 1101 14 1110 +1 0001 +2 0010 +3 0011 +4 0100 +5 0101 +6 0110 +7 0111 For this problem, set (ab)a-0. Conduct an exhaustive test in which you ex Conduct an exhaustive test in which you exercise all 256 possible combinations of a and b. Display one output line for each combination