Answered step by step

Verified Expert Solution

Question

1 Approved Answer

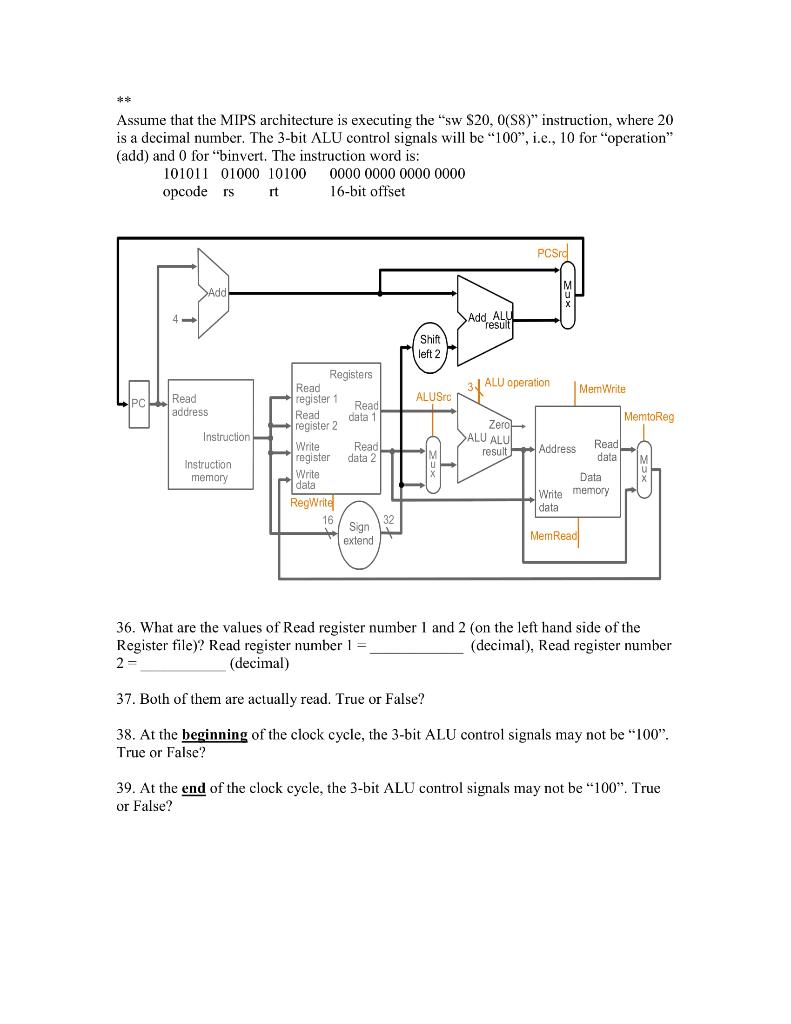

Assume that the MIPS architecture is executing the sw $20, 0($8) instruction, where 20 is a decimal number. The 3-bit ALU control signals will be

Assume that the MIPS architecture is executing the sw $20, 0($8) instruction, where 20 is a decimal number. The 3-bit ALU control signals will be 100, i.e., 10 for operation (add) and 0 for binvert. The instruction word is:

* :: Assume that the MIPS architecture is executing the sw $20.0(S8)" instruction, where 20 is a decimal number. The 3-bit ALU control signals will be "100", i.e., 10 for "operation" (add) and 0 for "binvert. The instruction word is: 101011 01000 10100 0000 0000 0000 0000 opcoders rt 16-bit offset PCSrd >Add >Add ALY result Shift left 2 ALU operation Mem Write Read address register 1 ALUSIN MemtoReg Zero SALU ALU Instruction Instruction memory Registers Read Read Read data register 2 Write Read register data 2 Write data RegWrite 16 Sign extend Read result Address data Data Write memory data MemRead 36. What are the values of Read register number 1 and 2 (on the left hand side of the Register file)? Read register number 1 (decimal), Read register number 2- (decimal) 37. Both of them are actually read. True or False? 38. At the beginning of the clock cycle, the 3-bit ALU control signals may not be "100". True or False? 39. At the end of the clock cycle, the 3-bit ALU control signals may not be "100". True or FalseStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started