Answered step by step

Verified Expert Solution

Question

1 Approved Answer

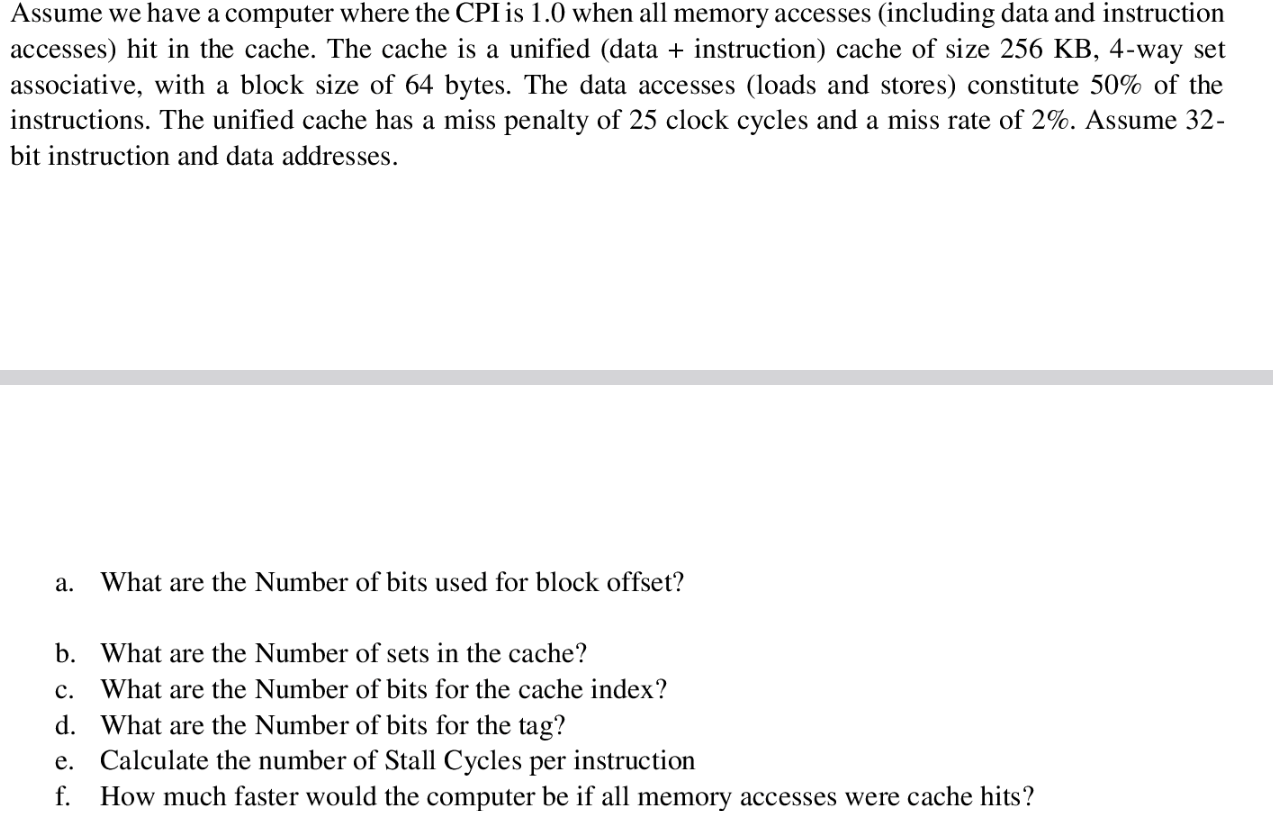

Assume we have a computer where the CPI is 1 . 0 when all memory accesses ( including data and instruction accesses ) hit in

Assume we have a computer where the CPI is when all memory accesses including data and instruction

accesses hit in the cache. The cache is a unified data instruction cache of size way set

associative, with a block size of bytes. The data accesses loads and stores constitute of the

instructions. The unified cache has a miss penalty of clock cycles and a miss rate of Assume

bit instruction and data addresses.

a What are the Number of bits used for block offset?

b What are the Number of sets in the cache?

c What are the Number of bits for the cache index?

d What are the Number of bits for the tag?

e Calculate the number of Stall Cycles per instruction

f How much faster would the computer be if all memory accesses were cache hits?

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started