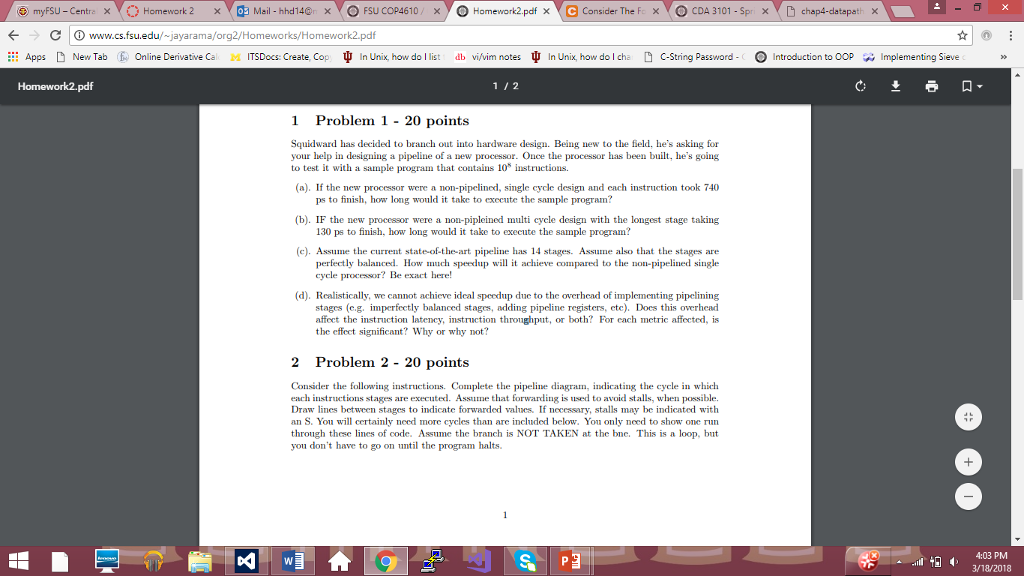

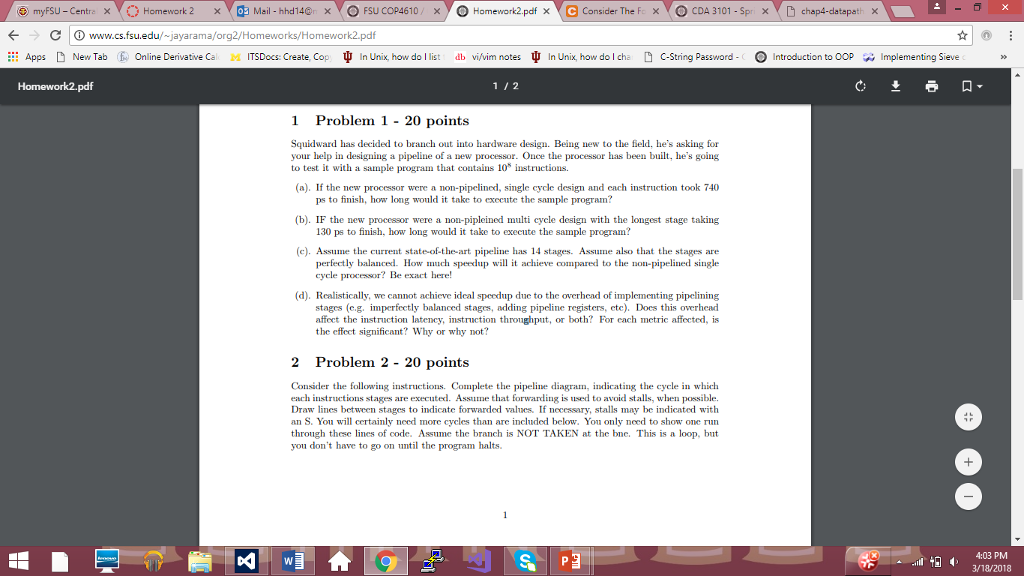

Can someone help me with part (b) and (c)?

Cwww.cs.fsu.edu/-jayarama/org2/Homeworks/Homework2.pdf Apps New Tab Online Derivative Ca M ITSDocs: Create, Cop In Unik, how do I list db vi/vim notesIn Unix, how do I cha C-String Password-Introduction to OOP Implementing Sieve Homework2.pdf 1 12 1 Problem 1 - 20 points Squidward has decided to branch out into hardware design. Being new to the field, he's asking for your help in designing a pipeline of a new processor. Ouce the processor has been bu, he's going to test it with a sample program that contains 10 instructions. (a). If the new processor were a non-pipelined, single cycle design and cach instruction took 740 ps to finish, how long would it take to execute the sample program? (b). IF the new processor were a non-pipleined multi cyce design with the longest stage taking 130 ps to finish, how long would it take to execute the sample program? (c). Assu the curent state-of-the-art pipeline has 14 stages Assu also that the stages are perfectly balanced How much speedup will it achieve compared to the non-pilined single cycle processor? Be exact here! (d). Realistically, we cannot achieve idcal speedup due to the overhead of implementing pipelining stages (c.g. imperfectly balanced stages, adding pipeline registers, etc). Does this overhead affoct the instruction latency, instruction throughput, or both? For cach metric affected, is the effect significant? Why or why not? 2 Problem 2 - 20 points Consider the following instructions. Complete the pipeline diagram, indicating the cycle in which each instructions stages are executed. Assume that forwarding is used to avoid stalls, when possible. Draw lines between stages to indicate forwarded values If ncessary, stalls may be indicated with an S. You will certainly need more cycles than are included blow. You only need to show one run through these lines of code. Assume the branch is NOT TAKEN at the bne. This is a loop, but you don't have to go on until the program halts. 4:03 PM 3/18/2018 Cwww.cs.fsu.edu/-jayarama/org2/Homeworks/Homework2.pdf Apps New Tab Online Derivative Ca M ITSDocs: Create, Cop In Unik, how do I list db vi/vim notesIn Unix, how do I cha C-String Password-Introduction to OOP Implementing Sieve Homework2.pdf 1 12 1 Problem 1 - 20 points Squidward has decided to branch out into hardware design. Being new to the field, he's asking for your help in designing a pipeline of a new processor. Ouce the processor has been bu, he's going to test it with a sample program that contains 10 instructions. (a). If the new processor were a non-pipelined, single cycle design and cach instruction took 740 ps to finish, how long would it take to execute the sample program? (b). IF the new processor were a non-pipleined multi cyce design with the longest stage taking 130 ps to finish, how long would it take to execute the sample program? (c). Assu the curent state-of-the-art pipeline has 14 stages Assu also that the stages are perfectly balanced How much speedup will it achieve compared to the non-pilined single cycle processor? Be exact here! (d). Realistically, we cannot achieve idcal speedup due to the overhead of implementing pipelining stages (c.g. imperfectly balanced stages, adding pipeline registers, etc). Does this overhead affoct the instruction latency, instruction throughput, or both? For cach metric affected, is the effect significant? Why or why not? 2 Problem 2 - 20 points Consider the following instructions. Complete the pipeline diagram, indicating the cycle in which each instructions stages are executed. Assume that forwarding is used to avoid stalls, when possible. Draw lines between stages to indicate forwarded values If ncessary, stalls may be indicated with an S. You will certainly need more cycles than are included blow. You only need to show one run through these lines of code. Assume the branch is NOT TAKEN at the bne. This is a loop, but you don't have to go on until the program halts. 4:03 PM 3/18/2018