Answered step by step

Verified Expert Solution

Question

1 Approved Answer

Change the module and the testbench of the problem 2 in a way that you are able to set the internal state of the registers

Change the module and the testbench of the problem in a way that you are able to set the internal state of the registers by loading the required PS values to the state registers and being able to read the NS of the registers. Problem refer to the image

a point

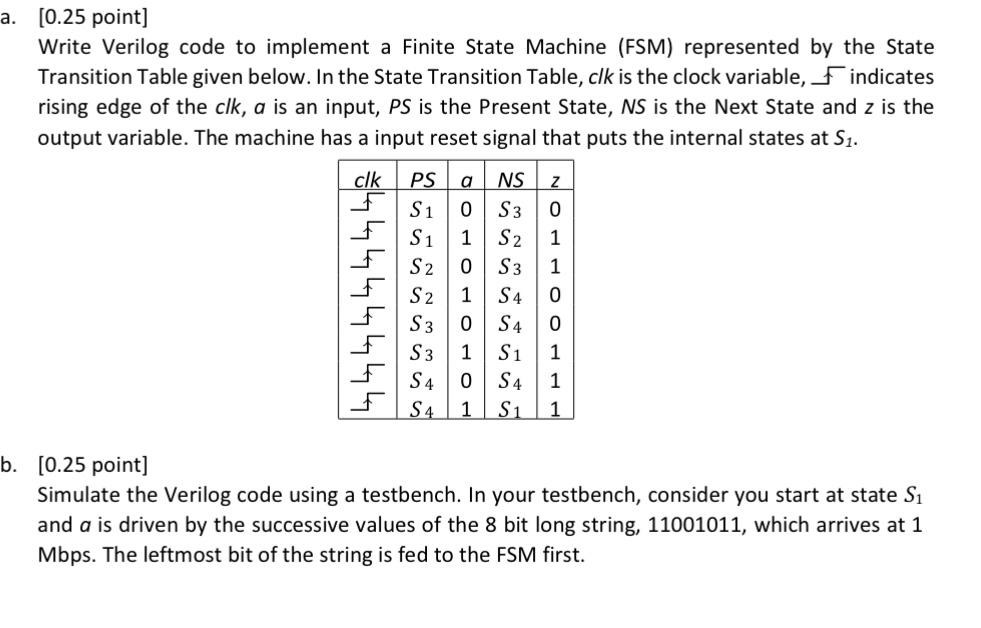

Write Verilog code to implement a Finite State Machine FSM represented by the State Transition Table given below. In the State Transition Table, clk is the clock variable, indicates rising edge of the is an input, PS is the Present State, NS is the Next State and is the output variable. The machine has a input reset signal that puts the internal states at

tableclk

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started