Question: choose the correct answer: 1.Using four cascaded CTR DIV 16, how many states must be deleted to achieve MOD 50,000? A) 50,000 B) 65,536 C)

choose the correct answer: 1.Using four cascaded CTR DIV 16, how many states must be deleted to achieve MOD 50,000? A) 50,000 B) 65,536 C) 25,536 D) 15,536 2.A bidirectional 4-bit shift register is storing the nibble 1110. The nibble 0111 is waiting to be entered on the serial data-input line (MSB is inserted first). After two clock pulses, the shift register is storing ________. A) 1110 B) 0111 C) 1000 D) 1001 3.The group of bits 10110111 is serially shifted (right-most bit first) into an 8-bit parallel output shift register with an initial state 11110000. After two clock pulses, the register contains ____________. A) 10111000 B) 10110111 C) 11110000 D) 11111100 4.What type of register would have a complete binary number shifted in one bit at a time and have all the stored bits shifted out one at a time? A) Parallel-in Parallel-out (PIPO) B) Parallel-in Serial-out (PISO) C) Serial-in Parallel-out (SIPO) D) Serial-in Serial-out (SISO) 5.How many states available in a 4-bit Johnson counter sequence? A) 1 B) 3 C) 4 D) 8 6.Which statement is FALSE? A) Johnson counter needs no decoder. B) n bit binary counter produce 2n states. C) The last output of Ring counter is connected to its first input. D) Ring counter is made of SISO registers. 7. What is a multiplexer? A) It is a type of decoder which decodes several inputs and gives one output. B) A multiplexer is a device that has many inputs and a single output. C) It takes one input and results into many outputs. D) It is a type of encoder which decodes several inputs and gives one output. 8. How many outputs are in a BCD decoder? A) 4 B) 5 C) 15 D) 10 9. In 1-to-4 demultiplexer, how many select lines are required? A) 2 B) 3 C) 4 D) 5 10. In a multiplexer the output depends on its ______________. A) data outputs B) select inputs C) select outputs D) rotate pin 11. Parity generators/checkers use which modulo summation? A) Modulo 8 B) Modulo 16 C) Modulo 2 D) Modulo 10 12. A code converter is a logic circuit that ________________________. A) Inverts the given input B) Converts into decimal number C) Converts data of one type into another type D) Converts to hexadecimal 13. Which of the following is NOT a latch? A) S-R latch B) T latch C) Gated S-R latch D) Gated D latch 14. The invalid state of active HIGH S-R latch occurs when _______________. A) S = 1, R = 0 B) S = 0, R = 1 C) S = 1, R = 1 D) S = 0, R = 0 15. The diagram below shows what type of temporary storage device?

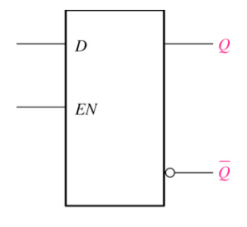

A) D flip flop B) C-D flip flop C) Gated S-R latch D) Gated D latch 16. Which of the following is considered as highest priority asynchronous input(s)?  17. When both inputs of a J-K pulse-triggered flip-flop are HIGH, and the clock triggers, what will the output be? A) An invalid state will exist. B) No change will occur in the output. C) The output will reset. D) The output will toggle. 18. Which statement is FALSE regarding universal bidirectional shift register (74HC194)? A) Can implement Serial In Serial Out (SISO) operation B) Can implement Serial In Parallel Out (SIPO) operation C) Can implement Parallel In Serial Out (PISO) operation D) Can implement Round Robin In Parallel Out (RRPO) operation

17. When both inputs of a J-K pulse-triggered flip-flop are HIGH, and the clock triggers, what will the output be? A) An invalid state will exist. B) No change will occur in the output. C) The output will reset. D) The output will toggle. 18. Which statement is FALSE regarding universal bidirectional shift register (74HC194)? A) Can implement Serial In Serial Out (SISO) operation B) Can implement Serial In Parallel Out (SIPO) operation C) Can implement Parallel In Serial Out (PISO) operation D) Can implement Round Robin In Parallel Out (RRPO) operation

D EN A. Clock B. PRE C. T D. J and K

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts